#### Министерство образования Российской Федерации Владимирский государственный университет Кафедра радиотехники и радиосистем

# МЕТОДИЧЕСКИЕ УКАЗАНИЯ К КУРСОВОМУ ПРОЕКТИРОВАНИЮ ПО ДИСЦИПЛИНАМ МИКРОПРОЦЕССОРНОГО ЦИКЛА

Составители А.И. НИКИТИН В.А. ЕГОРОВ

#### Владимирский государственный университет

## МЕТОДИЧЕСКИЕ УКАЗАНИЯ К КУРСОВОМУ ПРОЕКТИРОВАНИЮ ПО ДИСЦИПЛИНАМ МИКРОПРОЦЕССОРНОГО ЦИКЛА

#### Рецензент

#### Доктор технических наук, профессор Владимирского государственного университета

А.К. Бернюков

Печатается по решению редакционно-издательского совета Владимирского государственного университета

**Методические** указания к курсовому проектированию по дисциплинам микропроцессорного цикла / Владим. гос. ун-т; Сост.: А.И. Никитин, В.А. Егоров. Владимир, 2002. 44 с.

Содержат рекомендации по проектированию микропроцессорных вычислительноуправляющих устройств для решения задач радиоэлектроники по дисциплинам микропроцессорного цикла "Микропроцессоры и микроЭВМ", "Цифровые устройства и микропроцессоры", "Автоматизированные системы контроля и управления РЭС". Рассмотрены особенности и этапы проектирования микропроцессорных устройств на базе микропроцессоров фиксированной разрядности и однокристальных микроЭВМ — микроконтроллеров, приведены стандартные программно-аппаратные решения, варианты заданий и необходимые библиографические сведения.

Предназначены для студентов радиотехнических специальностей 200700 - радиотехника, 071500 - радиофизика и электроника, 201500 - бытовая радиоэлектронная аппаратура.

Табл. 2. Ил. 18. Библиогр.: 21 назв.

УДК 681.3(076.5)

#### **ВВЕДЕНИЕ**

Современное состояние и перспективы развития многих отраслей техники, в том числе и радиоэлектроники, во многом определяются широким проникновением средств вычислительной техники, использованием методов цифровой обработки информации.

В радиоэлектронике наряду с известными методами аналоговой обработки сигналов широкое распространение получили методы и устройства цифровой обработки, которые имеют целый ряд преимуществ.

Появление микропроцессоров (МП) открыло новые возможности цифровой обработки информации. Именно с появлением и развитием микропроцессорной техники связывают дальнейшее ускорение научнотехнического прогресса во многих отраслях промышленности. Применение цифровых микросхем и микропроцессоров в радиоэлектронных средствах (РЭС) существенно улучшает их технико-экономические показатели (потребление энергии, габариты, стоимость и т.д.), открывает широкие возможности реализации сложных алгоритмов управления и обработки сигналов.

Использование широких вычислительных возможностей микропроцессоров и систем на их основе позволяет приступить к реализации в РЭС многих оптимальных алгоритмов управления и обработки сигналов, ранее недоступных или отвергаемых из-за сложности и громоздкости аппаратуры.

Одним из ограничивающих факторов повсеместного использования МП в РЭС является их недостаточно высокое быстродействие, связанное с необходимостью последовательного выполнения команд программы. Однако создание специализированных цифровых процессоров обработки сигналов (ЦПОС), микроконтроллеров со встроенными ЦПОС позволяет в большинстве случаев снять это ограничение.

Применение микропроцессоров целесообразно в тех случаях, когда реализация определенных функций системы с использованием "жесткой логики" требует большого количества микросхем (более 30).

Обычно МП находят применение при построении широкого круга радиоэлектронных устройств, таких как радиотехнические измерители коор-

динат; сглаживающие фильтры вторичной обработки сигналов; вычислительные устройства бортовых навигационных комплексов; цифровые фильтры; устройства кодирования и декодирования сигналов; весовая обработка пачечных сигналов в радиолокации; различного рода устройства управления объектами и процессами; устройства измерения, контроля, диагностики и т.п.

Основная задача при выполнении курсового проекта (работы) - это усвоение основ построения и программирования специализированного микропроцессорного устройства (МПУ) для обработки информации и/или управления звеньями радиотехнических систем. В процессе выполнения курсового проекта (работы) студент должен получить представление по ряду проблем проектирования МПУ на аппаратно-программном уровне, приобрести навыки проектирования блоков микропроцессорных систем с использованием современной элементной базы.

Курсовая работа по дисциплинам "Цифровые устройства и микропроцессоры", "Микропроцессоры и микроЭВМ" выполняется одновременно с чтением соответствующего теоретического курса до его полного окончания. В связи с этим задание ограничивается проектированием сравнительно несложного микропроцессорного устройства (МПУ) на базе 8-битных МП типа КР580ВМ80А/КР1821ВМ85 (Intel8080/85), Z80 (Zilog), M6800, M6802, M6809 (Motorola), а также микроЭВМ серии К1816 (МК48, МК51, MCS-48, MCS-51 Intel).

#### СПИСОК УСЛОВНЫХ СОКРАЩЕНИЙ

АЛУ (Б) арифметическо-логическое устройство (блок)

АЦП (ЦАП) аналого-цифровой (цифро-аналоговый) преобразователь

БИС (СИС) большая (средняя) интегральная микросхема

ВУ внешнее устройство

ГТИ генератор тактовых импульсов

ЗУ (ОЗУ) запоминающее устройство (оперативное ЗУ)

ИМС интегральная микросхема

МК микроконтроллер

МП микропроцессор

МПК (МПС,У) микропроцессорный комплект (система, устройство)

ОМЭВМ однокристальная микроЭВМ

ПЗУ (ППЗУ) постоянное ЗУ (перепрограммируемое ПЗУ)

ПК персональный компьютер

ПАПИ программируемый адаптер параллельного интерфейса

ПКП программируемый контроллер прерываний

ПО программное обеспечение

РЭС радиоэлектронные средства (системы)

СК системный контроллер

УВВ устройство ввода-вывода

ЦП центральный процессор

ЦПОС цифровой процессор обработки сигналов

ЦПУ(Э) центральное процессорное устройство (элемент)

ША (ШД, ШУ) шина адреса (данных, управления)

ЭВМ (ПЭВМ) электронная вычислительная машина (персональная ЭВМ)

ЯА (ЯВУ) язык ассемблера (язык высокого уровня)

#### 1. ОБЩИЕ ВОПРОСЫ ПРОЕКТИРОВАНИЯ МИКРОПРОЦЕССОРНЫХ УСТРОЙСТВ

Наряду с известными преимуществами, которые вносят микропроцессорные средства в проектирование цифровых устройств обработки сигналов, измерения и управления объектами и процессами, имеется целый ряд проблем технического, психологического характера, осложняющих подходы к проектированию радиоэлектронных средств на базе микропроцессоров.

Общепризнано, что в основе трудностей, встречающихся на пути проектирования МПУ, лежит то обстоятельство, что такие устройства (системы) представляют собой совокупность как аппаратных, так и программных средств, которые должны рассматриваться в тесной и неразрывной связи.

К особенностям проектирования цифровых устройств на микропроцессорах можно отнести [2, 6, 9, 10, 16]:

- ◆ необходимость совместной разработки и отладки технических средств и программного обеспечения, ориентированных на конкретную совокупность решаемых функций;

- использование принципиально новых методов и средств разработки и отладки микропроцессорных систем по сравнению с традиционными методами и средствами;

- сильную взаимосвязь и даже интеграцию этапов проектирования, при которой разработчик должен одновременно обладать опытом проектирования микропроцессорных систем, а также разбираться в конкретной области их применения;

- ◆ обилие универсальных и специализированных микропроцессоров и других больших интегральных схем (БИС) в микропроцессорных комплектах (МПК), осложняющее процедуру оптимального выбора базового микропроцессора для проектируемого устройства;

- ◆ требование хорошего знания особенностей структуры и архитектуры большого количества микропроцессоров, БИС управления, БИС памяти и БИС интерфейсных компонентов.

#### 1.1. ЭТАПЫ ПРОЕКТИРОВАНИЯ МИКРОПРОЦЕССОРНЫХ УСТРОЙСТВ

Изменение элементной базы привело к изменению принципов проектирования вычислительных устройств, которые до появления микропроцессоров основывались на следующих положениях [6]:

- \* жесткая структура;

- \* последовательное и жесткое управление;

- \* линейная организация памяти;

- \* невозможность адаптации структуры к особенностям решаемой задачи.

На смену классическим принципам организации вычислительных систем приходят идеи проблемной ориентации систем, параллельной и конвейерной обработки информации, становится реальной идея создания адаптивно-перестраиваемых вычислительных и управляющих систем, конфигурация которых изменяется в процессе решения задачи для наиболее эффективной организации вычислительного процесса и обеспечения живучести системы. Дальнейшее развитие получают принципы модульности, магистральности и микропрограммируемости.

**Модульный** подход позволяет сократить время и затраты на проектирование системы, упрощает реализацию наращиваемости и реконфигурации системы, увеличивает время морального старения технических средств за счет модернизации (UPGRADE), упрощает контроль, эксплуатацию и ремонт устройств.

*Магистральный* способ организации связи между модулями системы позволяет упростить обмен информацией между блоками системы, обладает большей гибкостью и универсальностью, предоставляет большие воз-

можности по реконфигурации системы по сравнению с индивидуальными связями.

*Микропрограммное* управление повышает гибкость устройств, в большинстве случаев снижает стоимость блока управления по сравнению со схемами управления на "жесткой логике", упрощает контроль, повышает надежность за счет применения серийных специализированных БИС управления и БИС постоянной памяти.

Процесс проектирования микропроцессорной системы (МПС) включает в себя следующие этапы:

- системный;

- структурно-алгоритмический;

- отладочный;

- производственный.

Схематически процесс проектирования представлен на рис. 1. На рисунке видно, что процесс проектирования имеет ветвление по аппаратной и программной части.

#### 1.1.1. На этапе системного проектирования, исходя из требований к

программного обеспечения, а также связи между ними. В частности, выбираются микропроцессорные средства, подсистемы памяти, ввод-вывод и периферийные устройства.

Системное проектирование является в основном эвристическим. В результате работ на этом этапе проектирования создается так называемая функциональная схема МПУ.

При выборе микропроцессорных средств учитывают следующие факторы: производительность и разрядность микропроцессора, потребляемая мощность, число типов БИС в базовом микропроцессорном комплекте, климатические и механические параметры, стоимость, наличие опыта проектирования систем на основе выбираемых микропроцессорных средств.

Основным блоком МПК являются либо микропроцессоры с фиксированной разрядностью и фиксированной системой команд, либо микропроцессоры, представляющие собой микропрограммируемые микропроцессорные секции, имеющие разрядность от 2 до 16. В последнем случае параллельным соединением секций можно строить блоки обработки информации любой размерности, кратной разрядности секции. Набор команд в этом случае должен быть выбран проектировщиком в соответствии с конкретным назначением системы (алгоритмом реализуемых задач) и реализован микропрограммным способом. Микропрограммируемые МПУ характеризуются высокой производительностью, однако их сложность и высокая стоимость проектирования ограничивают область их применения задачами спецназначения, решаемыми коллективами опытных проектировщиков.

В последние годы в задачах управления, измерения, контроля и диагностики широкое применение получили однокристальные микроЭВМ (микроконтроллеры), в которых на кристалле кроме центрального процессора интегрированы запоминающие устройства (ОЗУ и ПЗУ) и различные периферийные устройства, включая ввод-вывод.

На системном этапе должно быть произведено разделение функций, которые будут реализованы аппаратными и программными средствами. Следует помнить, что, как правило, программная реализация функций приводит к уменьшению производительности и стоимости системы по сравнению с аппаратной реализацией этих функций.

**1.1.2.** На этапе структурно-алгоритмического проектирования используется функциональная схема микропроцессорной системы, разработанная на предыдущем этапе. Проектирование на втором этапе характери-

зуется широким использованием типовых схемных и программных решений с учетом их сильных взаимных связей.

При проектировании весьма эффективно могут применяться специализированные отладочные комплексы, которые позволяют без использования дополнительного оборудования разрабатывать и отлаживать программные и технические средства.

На структурном этапе производится окончательный выбор микропроцессорного комплекта или микроконтроллера. При этом необходимо учитывать следующие данные:

- состав БИС микропроцессорного комплекта;

- разрядность данных;

- количество обслуживаемых внешних устройств и методы обмена данными;

- время выполнения базовых команд;

- требуемый объем оперативной и постоянной памяти.

Кроме того, следует учитывать удобство математического обеспечения микропроцессора, т.е. систему команд и состав прилагаемых типовых подпрограмм (умножение, деление, тригонометрические преобразования и т.п.).

На этом этапе осуществляется детализация как программных, так и аппаратных схем и решений, их корректировка. В итоге создается окончательный вариант функциональной схемы вычислительного устройства, МПУ, функциональных схем устройств сопряжения, составляется рабочая программа, что позволяет уточнить объем ресурсов систем: объем памяти (ОЗУ и ПЗУ), время выполнения основных алгоритмов и наиболее критичных с точки зрения быстродействия участков программ.

На этапе параллельно разрабатываются и отлаживаются макетный образец и программное обеспечение МПУ в автономном режиме.

**1.1.3.** На **отладочном этапе** происходит окончательная аппаратно-программная отладка всей системы в целом, как правило, на специализированных отладочных комплексах. Здесь исправляются ошибки второго этапа и по итогам испытаний вносятся доработки как в схемные, так и в программные решения.

Имеются также возможности отладки и проверки принятых структурнотехнических и программно-алгоритмических решений до изготовления ма-

кета на универсальных ЭВМ и персональных компьютерах, на которых устанавливаются кросс-средства моделирования работы технических средств (аппаратной части МПУ) и отладки рабочих программ в режиме эмуляции на конкретном машинном языке микропроцессора.

**1.1.4.** На *производственном этапе* подготавливается техническая документация, образец изделия проходит установленные испытания, по результатам которых МПУ передается в производство.

## 1.2. ПРОЕКТИРОВАНИЕ ОСНОВНЫХ БЛОКОВ МИКРОПРОЦЕССОРНЫХ УСТРОЙСТВ

В этом разделе даются некоторые рекомендации по проектированию структурных и функциональных схем всей микропроцессорной системы и некоторых основных блоков. Приводятся некоторые схемные решения, которые могут быть взяты за образец.

#### 1.2.1. Центральное процессорное устройство обработки данных

Важным шагом при проектировании МПС является выбор того или иного микропроцессора или микроконтроллера для построения центрального процессорного устройства (ЦПУ), которое в основном определяет многие технические и схемные решения также и по другим аппаратным и программным компонентам системы.

На основании требований к микропроцессорной системе, основными из которых являются быстродействие, стоимость, потребляемая мощность, сложность алгоритмов обработки, производится первоначальный выбор типа ЦПУ.

Характеристики некоторых отечественных микропроцессоров и однокристальных микроЭВМ даны в [3, 4, 17 – 20].

Если требования по быстродействию системы не велики и в то же время алгоритмы обработки сигналов и управления достаточно сложны, то предпочтение может быть отдано однокристальным 8-разрядным микропроцессорам с фиксированной архитектурой, например, КР580ВМ80,

К1821ВМ85, Z80 [2, 6, 7, 8, 10]. Если поставлена задача оптимизации аппаратных затрат, потребляемой мощности и стоимости, то выбор может быть сделан в пользу также 8-разрядных микроконтроллеров МК48 или МК51 [16, 18].

Если требования по производительности системы весьма велики, то целесообразно обратиться к микропроцессорам и микроконтроллерам повышенной разрядности [15, 19]. Секционированные микропрограммируемые микропроцессоры в настоящее время практически не применяются ввиду значительных затрат как на разработку аппаратной части, так и программного обеспечения.

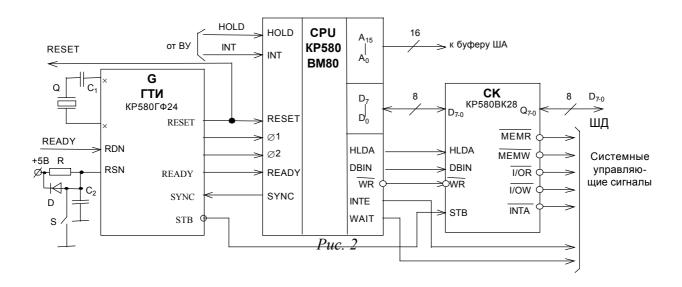

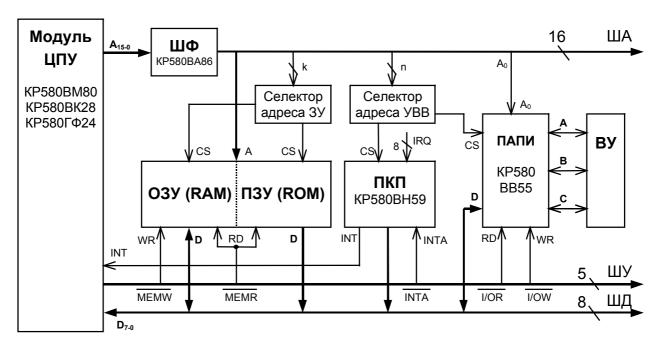

В качестве примера на рис. 2 показана схема подсистемы МПУ, состоящей из центрального процессора KP580BM80 (i8080), системного контроллера KP580BK28 и генератора тактовых импульсов (ГТИ) KP580ГФ24.

Микропроцессор К1821ВМ85 (i8085) объединяет на одном кристалле все БИС, показанные на рис. 2. Для того чтобы сохранить прежний тип корпуса, шина адреса в i8085 мультиплексируется с шиной данных.

Однокристальные микроконтроллеры представляют собой приборы, конструктивно выполненные в виде одной БИС, которая включает все составные части микроЭВМ: центральное процессорное устройство, память (программы и данные), а также программируемые интерфейсные схемы для связи с внешней средой.

Структурная организация, упрощенная и ориентированная на задачи управления система команд, специфически развитая организация вводавывода информации этих микросхем лучше всего приспособлены для решения задач управления и регулирования, а не для решения задач обработки данных.

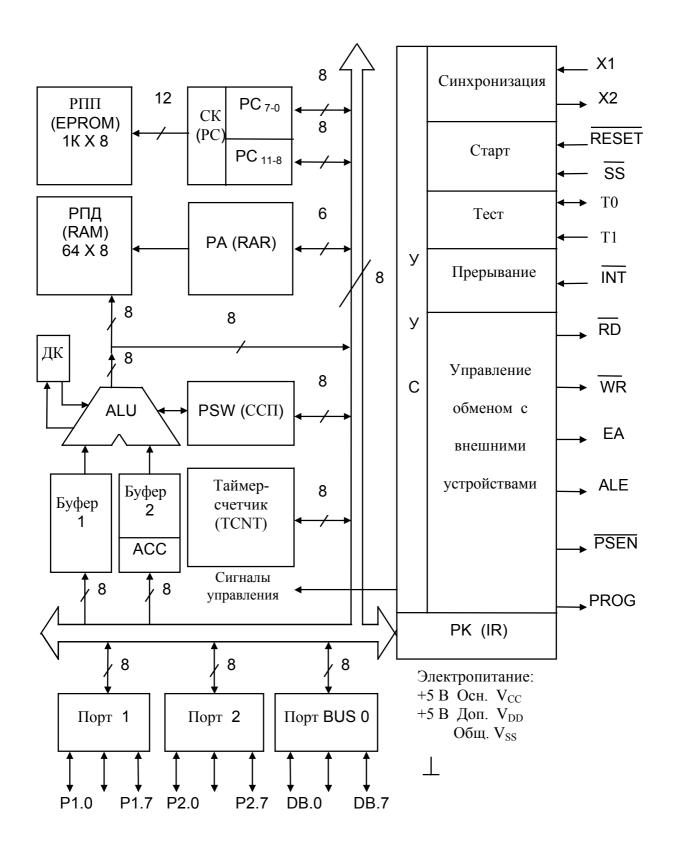

Структурная схема микроконтроллера МК48, в котором внутренняя двунаправленная 8-битная шина связывает между собой арифметическо-логический блок (АЛБ), устройство управления, память и порты вводавывода, приведена на рис. 3 [16, 17].

В отличие от наиболее распространенных микропроцессорных систем с архитектурой машин фон Неймана с общим адресным пространством программ и данных, в 8-разрядных микроЭВМ используется Гарвардская архитектура, в которой блоки ОЗУ (память данных) и ПЗУ (память программ) физически и логически разделены.

Это разделение дает существенные преимущества: ПЗУ намного превышает ОЗУ, а так как программа обращается чаще к ОЗУ, то сокращается размер адреса и команды и увеличивается быстродействие МЭВМ. Кроме того, производительность системы увеличивается, поскольку доступ к памяти программ и данных может быть независимым и одновременным.

*Puc. 3*

#### 1.2.2. Блок оперативной памяти

Характеристики некоторых БИС полупроводниковой оперативной памяти даны в [11, 13]. Следует помнить, что БИС ОЗУ могут быть статического и динамического типа. В последнем случае необходимо предусматривать циклическую регенерацию памяти с периодом не более 2 мс, что усложняет аппаратную часть системы.

Проектирование блока ОЗУ сводится к выбору типа БИС памяти и построению структурной схемы ОЗУ необходимой емкости и разрядности.

Для того чтобы построить память необходимой конфигурации, необходимо объединить ИМС, используя дешифраторы и логику управления ЗУ (с использованием входов выбора кристалла /CS).

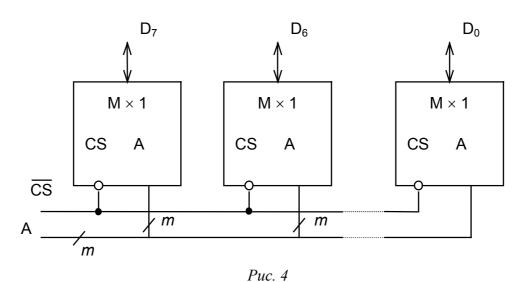

Для увеличения разрядности хранимых слов данных, используя однотипные ЗУ меньшей разрядности, их адресные и управляющие входы объединяются параллельно. На рис. 4 показана структура ЗУ М×8 на базе матричных ЗУ емкостью М×1, при этом число проводников в адресной шине  $m = \log_2 M$ .

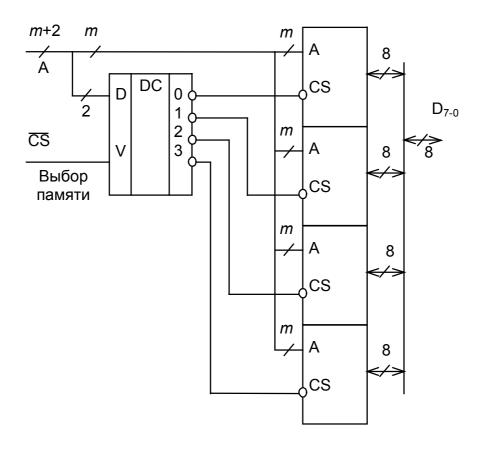

Для увеличения емкости ЗУ (адресного пространства) с сохранением разрядности хранимых слов необходимо объединить тристабильные выходы ИМС, а также младшие адресные линии; старшие адресные линии используются с помощью дешифратора для селекции отдельных микросхем

3У.

На рис. 5 показана структура ЗУ 4М×8 на базе четырех ИМС М×8, при этом младшие  $m = \log_2 M$  адресных линий ИМС объединены параллельно, а две старшие линии через ДШ с L – активными выходами включают по входам /СЅ отдельные ЗУ М×8. Полученное ЗУ представляет собой 4 банка памяти, каждый емкостью Мбайт. Адреса нулевого банка 0000...000 – 0011...111, адреса первого банка 0100...000 – 0111...111, адреса второго банка 1000...000 – 1011...111 и третьего банка 1100...000 – 1111...111.

На практике реализация памяти заданной структуры требует комбинации объединения ИМС с целью увеличения как разрядности, так и адресного пространства.

В микроконтроллерах также допускается наращивание памяти программ и памяти данных. Так, например, в МК51 память программ может быть увеличена до 64 кбайт и память данных также до 64 кбайт.

Puc. 5

#### 1.2.3. Блок постоянного запоминающего устройства

Для энергонезависимого и постоянного хранения программ и микропрограмм используют постоянные запоминающие устройства (ПЗУ). Как и ОЗУ, ПЗУ состоит из ячеек, обратившись к которым можно прочитать их содержимое. Отличие ПЗУ от ОЗУ состоит в том, что информация в ячейки ПЗУ записывается либо однократно, либо может быть модифицирована в результате специальной процедуры перепрограммирования (ППЗУ), после чего в штатном процессе эксплуатации используется лишь режим чтения (read only memory - ROM) [11, 13].

По способу занесения информации имеются *масочные* ПЗУ, программируемые предприятием-изготовителем, и ПЗУ, программируемые пользователем.

*Масочные ПЗУ*. Вначале формируются на кристалле все ЗЭ, затем по фотошаблону (маске) наносится требуемая сеть соединений. Для масочных ПЗУ характерна самая высокая степень интеграции и при большой серийности изделий это самые дешевые запоминающие устройства.

Программируемые (однократно) ПЗУ. Программирование пользователем производится с помощью специальных устройств – программаторов. В таком ПЗУ имеются *плавкие* перемычки, прожигание которых обеспечивает запись информации. В программировании здесь достаточно много проблем (сложный цикл программирования, высокий процент брака). Для программирования используются те же входы-выходы, которые служат для чтения информации.

Перепрограммируемые ПЗУ имеются двух типов: с электрическим и ультрафиолетовым стиранием информации.

Число циклов перепрограммирования составляет от нескольких десятков до нескольких тысяч. Гарантированное время хранения информации доходит до нескольких лет.

Проектирование блока ПЗУ схоже с проектированием ОЗУ. Однако, поскольку блок ОЗУ позволяет производить только считывание информа-

ции, то шина данных от блока ПЗУ может быть однонаправленной, что несколько упрощает организацию выборки и управления блоком ПЗУ.

#### 1.2.4. Проектирование интерфейса микропроцессорных систем

Под интерфейсом понимают совокупность шин, сигналов, электронных схем и алгоритмов, предназначенных для организации обмена информацией между блоками в системе, включая ввод-вывод.

Для организации связи между блоками МПС используют, как правило, систему коллективных шин (магистраль), которая включает в себя шину данных, шину адреса и шину управления. В микропроцессорных системах используется в основном так называемая асинхронная, замкнутая, связь.

Наиболее трудоемок и сложен процесс проектирования интерфейса с внешними устройствами для организации ввода-вывода.

Интерфейсные БИС подсистемы ввода-вывода представляют собой программируемые контроллеры, схожие по внутреннему устройству с ЦПУ, например, программируемый адаптер параллельного интерфейса К580BB55, программируемый адаптер последовательного интерфейса К580BB51.

Каждое интерфейсное устройство выполняет следующие действия:

- расшифровывает адрес, полученный от ЦПУ, и выделяет только то УВВ (ВУ), код которого совпадает с указанным адресом;

- декодирует код команды и организует ее выполнение;

- посылает в ЦПУ запрашиваемую информацию (готовность, сигналы прерываний и др.).

Работой системы в целом, в том числе обменом данными, по прежнему управляет центральный процессор, но он лишь инициирует работу периферийных адаптеров в требуемые моменты времени, а фактический обмен данными происходит под управлением соответствующих программируемых интерфейсных схем (контроллеров).

Интерфейсные компоненты бывают и непрограммируемыми, например, шинные формирователи (К589АП16, К580ВА86), регистры-защелки (К580ИР82).

Вопросы применения интерфейсных БИС для подключения внешних устройств достаточно описаны в литературе [2, 6-10, 14].

#### 1.3. СТРУКТУРНАЯ СХЕМА МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ

После выбора базового микропроцессорного комплекта, способа организации обмена и основных функциональных блоков системы можно приступить к разработке структурной схемы микропроцессорного устройства.

Типовая структурная схема МПУ на базе микропроцессора серии К580 представлена на рис. 6.

Puc. 6

Устройство содержит следующие основные блоки: модуль центрального процессорного устройства, состоящий из БИС ЦП, ГТИ и системного контроллера; подсистему памяти (ОЗУ и ПЗУ); подсистему ввода-вывода, представленную программируемым адаптером параллельного интерфейса (ПАПИ); подсистему прерываний на базе программируемого контроллера прерываний (ПКП), а также шинные формирователи (ША) адреса, селекторы адресов устройств ввода-вывода (УВВ) и запоминающих устройств (ЗУ) (непрограммируемые компоненты интерфейса системы). Рассматриваемая схема является минимальной и может быть расширена за счет введения дополнительных блоков, обеспечивающих последовательный ввод-вывод, прямой доступ к памяти и т.д. [3, 4, 8, 16, 18].

При построении простых МПУ можно отказаться от селекторов адреса (дешифраторов) и организовать необходимое управление с помощью старших линий шины адреса, которые не используются для адресации памяти.

Кроме функционального сопряжения необходимо обеспечить также и электрическое сопряжение компонентов МПУ. Условие правильного электрического сопряжения — это одинаковое представление логического нуля и единицы и обеспечение допустимой нагрузочной способности по каждому выходу микросхем.

При построении МПУ из компонентов только одного МПК первое условие обычно соблюдается. Однако чаще всего проектировщик сталкивается с ситуацией, когда необходимо использовать компоненты других МПК, а также различные ИМС малой и средней степени интеграции.

Условием правильного сопряжения компонентов является выполнение следующих неравенств:

$$U_1 \ge U_{1\min}$$

,  $U_0 \le U_{1\max}$ ,

где  $U_1$  ,  $U_0$  — напряжения логической единицы и нуля, а  $U_{1 \min}$  ,  $U_{1 \max}$  — допустимые значения этих величин.

При сопряжении биполярных БИС условием обеспечения нагрузочной способности являются неравенства:

$$I_1 \leq I_{1\max}$$

,  $I_0 \leq I_{0\max}$ ,

где  $I_{1\text{max}}$  ,  $I_{0\text{max}}$  – максимально допустимые токи на выходе БИС.

При сопряжении БИС, выполненных по МОП-технологии, нагрузочная способность определяется максимальной емкостью нагрузки  $C_{\rm H}$ , которую можно подключить к выходу БИС:

$$C_{\rm H} \leq C_{\rm Hmax}$$

.

Емкость  $C_{\rm H}$  складывается из входных  $C_{\rm BX}$  емкостей компонентов, подключенных к данному выходу БИС, а также емкостей монтажных соединений  $C_{\rm M}$  .

Как уже отмечалось, для повышения нагрузочной способности шин можно использовать шинные формирователи, приемопередатчики.

#### 1.4. РАЗРАБОТКА ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ

Разработку программного обеспечения (ПО) можно разделить на несколько этапов:

- 1. *Постановка задачи*. На этом этапе формализуется задача. Сюда входит определение сущности процессов обработки информации, формулирование системных ограничений (время выполнения, точность, время реакции) и разработка методов обработки ошибок;

- 2. *Разработка алгоритма*. Выбирается метод решения задачи, разрабатывается структурная схема алгоритма с использованием методов структурного и модульного программирования, проектирования программного обеспечения сверху вниз;

- 3. *Разработка программы*. Создается программа в машинных кодах, а также необходимые микропрограммы (в случае проектирования микропрограммируемого МПУ);

- 4. *Отпадка и документирование*. Осуществляются поиск и исправление программных ошибок. В заключение разрабатывается программная документация, которая дает возможность разобраться в работе программного обеспечения с целью расширения и модернизации.

Критериями оценки качества разрабатываемого ПО могут быть надежность, скорость работы, простота использования, устойчивость по отношению к ошибкам, расширяемость, стоимость программирования.

При выборе языка программирования следует иметь в виду следующее. Текст программы на *языке ассемблера* (ЯА) содержит в 4 – 10 раз больше строк, чем текст эквивалентной программы на *языке высокого уровня* (ЯВУ). Программы, написанные на ЯВУ, обычно занимают на 50 – 200 % больше памяти и требуют для своего выполнения на 50 – 300 % больше времени, чем программы, написанные на ассемблере опытным программистом [5, 6].

При разработке ПО важно внимательно провести распределение памяти. Процессорно зависимая область включает небольшое количество ячеек для обслуживания прерываний и функций ввода-вывода, резервируемая область адресов памяти предназначена для размещения таблиц переходов, стеков, параметров программ. Область временного хранения служит для кратковременного запоминания промежуточных результатов. В области резидентных программ размещаются постоянно хранимые в ЗУ программы:

мониторы, загрузчики, трансляторы. Как правило, эта часть ПО размещается в ПЗУ или ППЗУ.

Для разработки ПО микропроцессорных систем широко используются программные кросс-средства, установленные на платформах персональных компьютеров и систем проектирования МПС. К числу таких кросс-средств можно отнести программную продукцию фирм Avocet, Intel, эмуляторы-отладчики Z80MU и др. Производство практически всех микропроцессоров и микроконтроллеров в настоящее время сопровождается программно-аппаратной поддержкой для разработки МПС на базе персональных компьютеров.

В литературе [1, 5, 6, 8, 14 - 17] имеется много примеров фрагментов программ, написанных на языке ассемблера МП К580 и МК48, 51. Здесь же приведены системы команд процессоров и временные параметры исполнения отдельных команд.

#### 2. СОДЕРЖАНИЕ И ПОРЯДОК ВЫПОЛНЕНИЯ КУРСОВОГО ПРОЕКТА (РАБОТЫ)

В первом разделе методических указаний рассматривались общие вопросы и этапы проектирования аппаратных и программных средств микропроцессорных устройств. Выполнение всех этапов проектирования в полном объеме требует больших затрат времени и труда высококвалифицированных специалистов.

Безусловно, в рамках студенческого курсового проекта нельзя рассчитывать на более или менее полное решение всех вопросов проектирования. Тем не менее в процессе выполнения курсового проекта студент должен получить представление по ряду проблем проектирования МПУ на аппаратно-программном уровне, приобрести навыки проектирования блоков микропроцессорных систем с использованием современной элементной базы.

Внимание в работе должно быть равным образом акцентировано как на проектирование аппаратных средств, так и на разработку резидентного

**программного обеспечения.** Возможно, что при этом доля программного обеспечения по трудозатратам значительно превысит затраты на аппаратные средства. Условием успешного решения поставленной задачи служит завершенность проекта и возможность его практической реализации.

#### 2.1. СОДЕРЖАНИЕ КУРСОВОГО ПРОЕКТА (РАБОТЫ)

**Задание:** спроектировать микропроцессорное вычислительное устройство для обработки информации и/или управления в составе радиотехнической (контрольно-измерительной) системы.

**Исходные** данные для проектирования взять в приложениях 1 и 2 с учетом модификации параметров заданий для группы. Любой вариант в группе может быть выбран только один раз, приоритет при выборе варианта принадлежит студенту с таким же номером в журнале группы.

**В результате проектирования** должна быть разработана структурная схема МПУ; рассмотрено функциональное и электрическое сопряжение компонентов МПУ; выбрана элементная база для реализации блоков МПУ и разработана принципиальная схема устройства; составлена блок-схема алгоритма и программа, реализующая заданную процедуру с учетом расчетных временных соотношений.

#### 2.2. ПОРЯДОК ВЫПОЛНЕНИЯ КУРСОВОГО ПРОЕКТА (РАБОТЫ)

Следует помнить, что любой процесс проектирования не может быть полностью алгоритмизирован и формализован, он должен включать в себя творческое начало и разумную инициативу. Научить искусству проектирования нельзя, но научиться этому можно. Рекомендации, содержащиеся в данной работе, нельзя рассматривать как догму.

Тем не менее можно рекомендовать следующий порядок проектирования:

- 1. Анализ исходного задания, выбор базового микропроцессора.

- 2. Изучение структуры и особенностей функционирования выбранного микропроцессора и других компонентов, в частности подсистем памяти и ввода-вывода.

- 3. Проработка функционального и алгоритмического сопряжения основных блоков устройства, разработка структурной схемы, включая интерфейсные звенья.

- 4. Разработка электрической принципиальной схемы МПУ. При этом продумать вопрос об инициализации (начальном запуске системы), оценить состав программного обеспечения и распределить память, определить физические адреса портов ввода/вывода и/или интерфейсных схем. Особое внимание уделить корректному подключению ЦАП-АЦП, в том числе правильному масштабному соотношению кодов вводимых и выводимых чисел с диапазоном и полярностью сигнала. Для курсового проекта предусматривается разработка печатной платы устройства.

- 5. Составление алгоритма (блок-схемы) и программы конкретной процедуры на языке ассемблера выбранного микропроцессора, принимая во внимание расчет времени выполнения участков программ и других временных соотношений в функции от заданных параметров сигналов и процессора (тактовой частоты).

- 6. Оформление текстовой части пояснительной записки и графического материала.

#### 2.3. ОФОРМЛЕНИЕ КУРСОВОГО ПРОЕКТА (РАБОТЫ)

**Расчетно-пояснительная записка** объемом 15 – 20 страниц (включая рисунки и схемы в тексте) оформляется в соответствии со стандартом предприятия и включает в себя:

- титульный лист обложку;

- полностью оформленный и подписанный бланк задания;

- оглавление со ссылками на страницы пояснительной записки;

- анализ технического задания;

- выбор и обоснование структурной схемы устройства;

- выбор и обоснование принципиальной схемы устройства;

- описание алгоритма по разработанной блок-схеме с пояснениями;

- программу на языке ассемблера и в машинных кодах с содержательными комментариями;

- схемы, графики и временные диаграммы, поясняющие решение;

- перечень элементов по ГОСТ;

• библиографический список использованной литературы с указанием ссылок в тексте (не менее 5 – 6 наименований).

Объем пояснительной записки может меняться в зависимости от характера задачи проектирования (курсовая работа или проект).

**Графическая часть** курсового проекта (работы) представляет собой принципиальную схему МПУ, выполненную на листе формата А3 (А2) и чертеж печатной платы устройства (только для проекта).

#### 3. ОСОБЕННОСТИ РАЗРАБОТКИ ПРОГРАММНО-АППАРАТНЫХ СРЕДСТВ МИКРОПРОЦЕССОРНЫХ УСТРОЙСТВ

В данном разделе приводятся практические рекомендации и некоторые инженерные решения по разработке аппаратных средств и программного обеспечения для типовых заданий в соответствии с изложенными во второй главе требованиями к курсовому проекту (работе).

#### 3.1. АППАРАТНАЯ ЧАСТЬ

Предполагается, что основная часть студентов выберет в качестве базового микропроцессорный комплект К580, по использованию которого имеется достаточный объем учебной и технической литературы. Вопросы разработки и исследования микропроцессорных систем на базе МП КР580ВМ80 отражены также в лекционном материале и лабораторном практикуме.

Следует отметить, что МП i8080 морально и технически к настоящему времени устарел и в новых изделиях не применяется. Однако идеи, заложенные фирмой Intel в этот первый и ставший классическим 8-разрядный микропроцессор, были настолько удачными, что нашли применение в последующих разработках как микропроцессоров, так и микроконтроллеров многих фирм.

Архитектурные решения, заложенные в семейство микропроцессоров Intel 80/85, были использованы также и в построении процессоров цифровой обработки сигналов (ЦПОС) [19, 20]. Можно сказать, что МП i80/85 представляют собой связующее звено для трех основных направлений развития процессорной техники: МП, МК и ЦПОС. В этой связи использова-

ние МПК К580 и других 8-разрядных микропроцессоров этого класса (i8085, Z80) в учебных целях вполне оправдано и актуально.

#### 3.1.1. Процессорный модуль и распределение памяти

Типовое построение модуля ЦПУ с использованием МПК К580 на уровне принципиальных схем представлено в [3, 4, 8 – 10, 16, 17]. При использовании МП К1821М85 (i85) и Z80 построение процессорного модуля упрощается, так как здесь не требуется системный контроллер и в ряде случаев можно обойтись без шинных формирователей адреса.

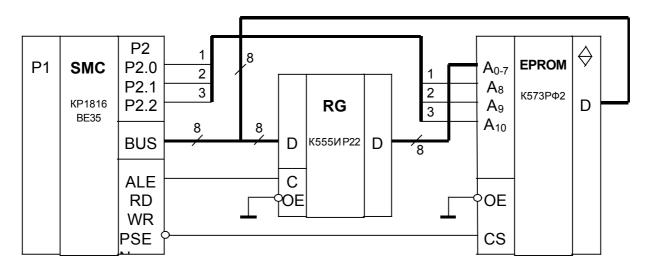

Еще более простым выглядит построение процессорного блока на базе микроконтроллеров семейства К1816 (МК48, МК51), в которых на одном кристалле интегрирована подсистема памяти (ОЗУ и ПЗУ) и устройства ввода-вывода. Следует отметить, что не во всех МК имеется встроенное ПЗУ (память программ). На рис. 7 показана схема подключения внешнего ПЗУ к МК48 (КР1816ВЕЗ5). Микропроцессорные устройства с таким построением наиболее удобны для отладочных версий изделий.

*Puc.* 7

Одиннадцатиразрядный адрес ячейки памяти ППЗУ с ультрафиолетовым стиранием К573РФ2 выводится из МК через два параллельных порта BUS и P2, при этом восемь младших бит адреса сигналом /ALE запоминаются в регистре-защелке К555ИР22. После этого шина BUS переходит в режим ввода и процессор читает байт из ППЗУ по сигналу /PSEN.

Важным моментом в проектировании аппаратной части МПУ на базе микропроцессоров (машин фон Неймана) является распределение адресного поля между ОЗУ, ПЗУ и УВВ.

Если ЗУ имеет емкость  $2^k$  слов байт, для адресации его ячеек используется k линий шины адреса:  $A_0$  -  $A_{k-1}$ . Селекция БИС ОЗУ или ПЗУ осуществляется с помощью одной из неиспользованных линий ША, подключаемых к входам выбора кристалла /CS, например,  $A_{15} = 0$  может соответствовать ОЗУ, а  $A_{15} = 1 - \Pi$ ЗУ. Схема селектора адреса ЗУ (см. рис. 6) сводится при этом к одному инвертору.

Для селекции портов ввода-вывода обычно используются младшие разряды ША. В МПУ на базе МПК К580 по команде ввода-вывода IN (OUT) выставляется 8-разрядный адрес одновременно как на младшей половине ША, так и на старшей половине ША. Применение одних и тех же адресов и линий ША для ЗУ и УВВ возможно, поскольку обращение к этим устройствам осуществляется с помощью разных управляющих системных команд МП (/МЕМR, /МЕМW, /IOR, /IOW).

Если в качестве портов применяются многорежимные буферные регистры типа К589ИР12 и число их не превышает восьми, то каждому порту ставится в соответствие одна линия ША, по которой передается сигнал /СЅ выбора данного порта. Иными словами, каждый порт кодируется унитарным кодом. Если портов более восьми (в МПС на базе КР580ВМ80 — 9 ... 256), они селектируются различными двоичными кодами и для построения селектора выбора УВВ используется дешифратор.

Если в качестве портов ввода-вывода применяются программируемые адаптеры (параллельные и последовательные), то максимальное число портов оказывается несколько меньше 256, так как некоторая часть адресного поля отводится для адресации служебных регистров. Здесь также возможно селектировать адаптер унитарным кодом.

Так, например, для селекции программируемых адаптеров ПАПИ КР580ВВ55 можно использовать любой из шести разрядов  $A_7$  ...  $A_2$  ША (два младших бита ША  $A_0$  и  $A_1$  зарезервированы для адресации внутренних регистров ПАПИ). Таким образом, без дополнительных схем селекции адреса УВВ можно использовать в МПС до шести адаптеров подобного типа.

Далее при распределении адресного пространства необходимо выделить в ПЗУ область для размещения основной программы и подпрограмм

(в том числе подпрограмм обработки прерываний), констант, таблиц, массивов данных и т.д. Начало основной программы зависит от наличия каких-либо системных программных средств, например программы-монитор. В случае отсутствия даже простейших управляющих программ начальный сброс (RESET) должен приводить к загрузке в программный счетчик адреса начала основной программы. В МПУ на базе КР580ВМ80 сброс МП приводит к занесению в счетчик команд РС=0000h. Целесообразно по этому адресу поместить команду безусловного перехода к началу основной программы, так как начиная с адреса 0000h по 0003Fh первые 64 ячейки памяти отведены под вектора системы прерываний и, следовательно, не должны использоваться никакой прикладной программой.

В ОЗУ выделяются области для хранения поступающих из процессора и УВВ данных и промежуточных результатов, а также для организации стека; начало (вершина) стека часто располагается в последней ячейке ОЗУ.

#### 3.1.2. Подключение внешних устройств

#### Цифро-аналоговый (аналого-цифровой) преобразователь

В значительном числе вариантов заданий (прил. 1) необходимо преобразование цифровой информации в аналоговую форму или аналоговой информации в цифровой код, т.е. использование ЦАП (АЦП). Аналоговым сигналом является напряжение положительной и отрицательной полярности, а цифровой сигнал чаще всего представлен двоичным параллельным кодом, разрядностью не более восьми.

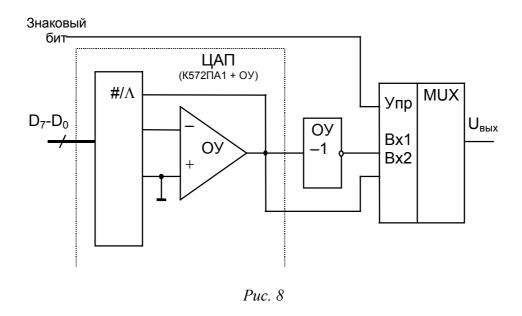

В номенклатуре серийных отечественных ЦАП-АЦП преобладают 10-16—разрядные устройства. Определенную проблему представляет также получение биполярного выходного сигнала МПУ на базе более дешевых и простых униполярных ЦАП. На рис. 8 показана функциональная схема биполярного преобразователя "цифра-аналог" на базе ЦАП К572ПА1.

Пунктиром обведена схема стандартного включения ЦАП К572ПА1 с внешним операционным усилителем (ОУ). С помощью другого ОУ получено напряжение противоположного знака по отношению к выходному сигналу ЦАП. С учетом знакового бита на выходе аналогового мультиплексора (типа 561КП1, 564КП2) формируется биполярный сигнал  $U_{\rm вых}$ . Из десяти разрядов ЦАП К572ПА1 используется 7 — 8 старших разрядов, вес входного младшего значащего разряда  $D_0$  при этом увеличивается в  $2^2 - 2^3$  раз.

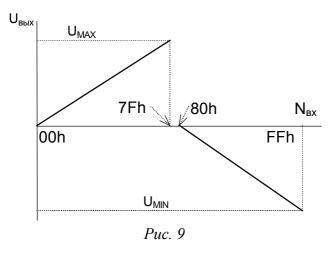

Если цифровой сигнал представлен прямым кодом (знаку "минус" соответствует логическая единица, а знаку "плюс" — логический ноль), то для ЦАП, показанного на рис. 8, передаточная характеристика  $U_{\text{вых}} = f(N_{\text{вх}})$  выглядит как показано на рис. 9.

Примеры подключения ЦАП и АЦП приведены в [12, 13, 18]. Во

всех случаях для правильного понимания работы преобразователей необходимо приводить передаточную характеристику "Вход – выход".

#### Обнаружитель внешних событий

Под внешним событием здесь понимается перепад уровня сигнала из "0" в "1" (переднего фронта) или из "1" в "0" (заднего фронта), установление низкого или высокого потенциала, появление одного или нескольких импульсов и т.д.

Такие задачи возникают при измерении длительности, периода или частоты сигналов, при обработке бинарной информации от датчиков сигналов, а также для формирования временных интервалов при управлении объектами.

Некоторые из описанных выше событий могут быть обнаружены чисто программным способом, обнаружение другой части требует аппаратной поддержки вследствие недостаточного быстродействия процессорной обработки входных сигналов.

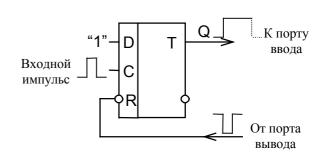

На рис. 10 показана схема, позволяющая обнаружение импульсов произвольной длительности, в том числе коротких, свести к обнаружению потенциала. Входной импульс, подлежащий обнаружению и длительность которого достаточна для срабатывания D-триггера, устанавливает выходной сигнал Q равным логической единице. Этот уровень подается на один из входов УВВ в качестве сигнала готовности. Наличие этого сигнала обрабатывается

Puc. 10

программно или же он вызывает подпрограмму обработки прерываний. В любом случае реакцией МПУ на сигнал Q=1 будет сигнал обратной связи с одного из выходов порта вывода, сбрасывающий триггер в нулевое состояние, после чего схема вновь готова к приему очередного импульса.

Единственный вектор прерываний RST 7 (0038h) можно получить с помощью системного контроллера КР580ВК28 (КР580ВК38) без дополнительных компонентов [4]. Для этого необходимо подключить его вывод /INTA (см. рис. 2) к источнику питания +12В через сопротивление 1 кОм. Во время действия сигнала DBIN системный контроллер формирует на шине данных код команды RST 7.

#### Индикация результатов

В некоторых вариантах заданий предусматривается вывод результатов обработки информации в цифровой форме.

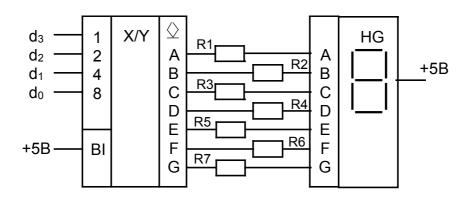

Если выводимая информация должна быть представлена десятичным кодом, то перед выводом на индикацию или в процессе обработки следует преобразовать числа из двоичного представления в двоично-десятичный код (ВСD). В случае вывода двоичной информации целесообразно индицировать данные в шестнадцатеричном коде. На рис. 11 показана схема индикации одной цифры (половина байта) в ВСD — коде с использованием семисегментных индикаторов.

В качестве преобразователя X/Y двоично-десятичного кода в семисегментный код можно использовать ИМС К514ИД2, а для индикации цифры HG – АЛС314, АЛС 324.

Для визуальной регистрации чисел в 16-ричной системе счисления следует использовать преобразователи кодов на базе ПЗУ типа К155РЕЗ или К556РТ4 [21].

Puc. 11

#### 3.2. ПРОГРАММНАЯ ЧАСТЬ

Программа, решающая поставленную задачу практически во всех вариантах, не превышает 100 команд на языке ассемблера выбранного микропроцессора, поэтому в примерах, приводимых в этом разделе, используется язык ассемблера МП КР580ВМ80, но без директив (псевдокоманд). При отладке программ на ПЭВМ, имеющих кросс-средства трансляции и отладки, программы необходимо дополнить соответствующими псевдокомандами.

#### 3.2.1. Типовые решения в технике программирования

В этом разделе рассмотрены вопросы организации циклов ожидания, задержки, поллинга (опроса) и программируемого ввода-вывода.

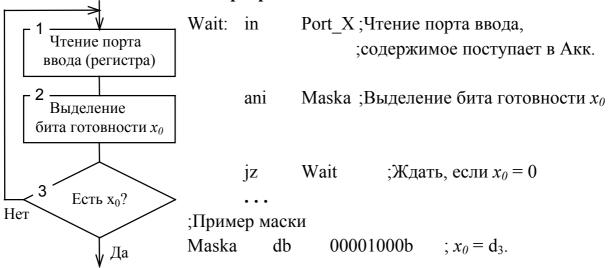

#### Цикл ожидания при вводе

Начало выполнения программы часто определяется моментом появления сигнала готовности некоторого УВВ, до этого события программа должна находиться в состоянии ожидания. Блок-схема алгоритма цикла ожидания, в котором проверяется сигнал готовности (осведомительный сигнал) внешнего устройства, показана на рис. 12.

#### Программа цикла ожидания

Puc. 12

#### Организация задержки

Задержка может быть организована как с помощью одного простого цикла, так и сложным образом с использованием двух и более циклов, как показано на рис. 13.

Параметр внешнего цикла заносится до начала формирования задержки. В качестве счетчиков циклов используются регистры процессора.

#### Программа задержки

;Инициализация счетчика внешнего цикла

mvi b,K Vnesh

;Инициализация счетчика внутреннего цикла

Vnesh: mvic,K\_Vnutr;(7)

Vnutr: dcr c ;(5) Повтор внутреннего

jnz Vnutr ;(10) цикла

dcr b ;(5) Повтор внешнего

jnz Vnesh ;(10) цикла

В круглых скобках приведены длительности выполнения команд в тактах  $T_{\theta}$  основной тактовой частоты. Длительность задержки при этом

определяется по формуле

$$t_3 = T_0 (5+10) K Vnesh [7+(5+10) K Vnutr].$$

Подбирая параметры циклов, можно получить требуемую длительность задержки  $t_3$  .

#### Сканирование (поллинг) слова готовности УВВ

Биты готовности данных от нескольких УВВ могут быть сгруппированы в одно или несколько слов. Основная программа поочередно опрашивает (сканирует) значения битов из слова готовности УВВ и при необходимости вызывает подпрограмму обработки запроса, соответствующую установленному биту готовности конкретного УВВ. Фрагмент блок-схемы алгоритма поллинга приведен на рис. 14.

|       | Ι         | Ірограг     | мма поллинга                                                      |    | Начало                     |

|-------|-----------|-------------|-------------------------------------------------------------------|----|----------------------------|

| Scan: | in<br>mov | STAT<br>b,a | Е;Чтение слова готов-<br>;ности и сохранение<br>;его в регистре В |    | Чтение слова овности STATE |

|       | ani       | 01          | ;Анализ бита готов-<br>;ности УВВ № 1                             | <2 | УВВ №1 Да готово?          |

|       | cnz       | SR1         | ;Вызов подпрограммы<br>;обработки запроса<br>;УВВ № 1             |    | Нет Вызов п/п №1           |

|       | ani       | 02          | ;Анализ бита готов-<br>;ности УВВ № 2                             | <4 | УВВ №2<br>готово ? Да      |

|       | cnz       | SR2         | ;Вызов подпрограммы<br>;обработки запроса<br>;УВВ № 2             |    | Нет Бызов п/п №2           |

| •••   | ani       | k           | ;Анализ бита готов-<br>;ности УВВ № k                             | <6 | УВВ №k Да готово ?         |

| •••   | cnz       | SRk         | ;Вызов подпрограммы ;обработки запроса ;УВВ № k                   |    | Нет Вызов п/п №k  Рис. 14  |

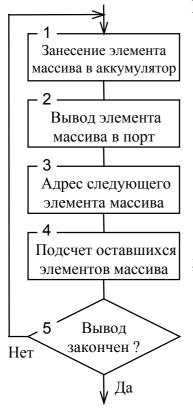

#### Вывод массива данных во внешний порт

Участку программы, выводящему данные во внешний порт (адаптер), должны предшествовать команды инициализации адаптера (см. далее) и занесение адреса начала массива в одну из регистровых пар (ВС, DE, HL), с помощью которой будут адресоваться элементы массива (ячейки памяти), а также инициализация счетчика числа элементов массива. Блок-схема алгоритма вывода данных приведен на рис. 15.

Puc. 15

#### Программа вывода массива данных в порт

Go\_on: mov a,m ;Массив адресуется [HL] ;Возможно использование команд LDAX В ;или LDAX D

out Port\_Y ;Вывести элемент массива ;в порт Port Y

inxh ;3десь могут быть также ;INX В или INX D

dcr c

;Регистр С инициирован числом элементов массива

jnz Go\_on ;Продолжить, если не все ;элементы массива ;выведены

При выводе массива данных во внешний порт по аналогии с обращением к памяти схема алгоритма не меняется; необходимо адресовать массив

одной регистровой парой, а порт (регистр) – другой. В качестве порта вывода может быть и ЦАП.

Программа вывода может выглядеть следующим образом:

BCL: mov а,m ;Элемент массива данных переслать в аккумулятор stax d ;и загрузить его в порт (память) по адресу [DE] inx h ;Адрес следующего элемента dcr c inz BCL ;Продолжить, если вывод не закончен

Длительности исполнения участков программ можно подсчитать, используя значения длительностей команд в числах тактов. Системы команд и длительности их исполнения даны в [1, 3, 4, 8]. Значения периода  $T_0$  генератора тактовых импульсов приведены в прил. 1.

#### 3.2.2. Формирование сигналов во времени

В этом разделе предполагается, что в качестве портов ввода-вывода используется ПАПИ КР580ВВ55, а преобразование "код-аналог" производится с помощью ЦАП К572ПА1 (см. рис. 8, 9).

Параллельный адаптер можно селектировать по входу /CS без дешифрации адресных линий, если число подключаемых таких интерфейсных схем не превышает шести. Любая линия  $A_7...A_2$  может играть роль сигнала выбора кристалла. Если взять /CS =  $A_3$ , тогда порты адаптера будут иметь адреса:  $A \rightarrow F4h$  (11110100b),  $B \rightarrow F5h$ ,  $C \rightarrow F6h$ , а адрес регистра управления F7h.

#### Непрерывная импульсная последовательность

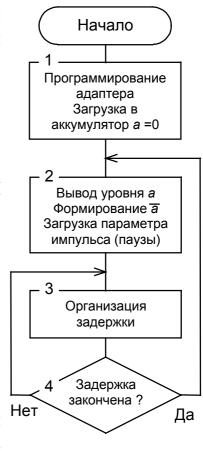

Пусть для определенности необходимо формировать последовательность импульсов частотой f=1 кГц, скважностью q=2 (меандр) и уровнями a=0 и 1. Блок-схема алгоритма меандра представлена на рис. 16. В аккумулятор загружается уровень  $a\in\{0,1\}$ , в регистре В организуется счетчик.

#### Программа формирования меандра

MNDR: mvi ;(7) Программирование ПАПИ a,81h 0F7h ;(10) Загрузка управл. слова out (7)  $a = 0 \rightarrow в$  аккумулятор a.0 mvi M1: 0F5h (10) Вывод a = 0 в порт В out (4) A  $\leftarrow$  (/A), инверсия A cma mvi b,K ;(7) К - параметр задержки M2: dcr b ;(5) Организация задержки jnz M2;(10)M1 ;(10) Продолжить jmp ;формирование

В круглых скобках приведены длительности выполнения команд в тактах  $T_{\theta}$ . Общее количество тактов во внешнем цикле, определяющем дли-

Puc. 16

тельность импульса или паузы (0 или 1), равно

$$N_i = 10 + 7 + 4 + 10 + (5 + 10) K = 31 + 15K.$$

При стандартной тактовой частоте для МП КР580ВМ80  $f_0 = 2$  МГц период следования генерируемого сигнала будет (мкс)

$$T = 2N_iT_0 = 2N_i/f_0 = 31 + 15K$$

.

Отсюда f=1 /  $T=10^3$  / (31 + 15K), к $\Gamma$ ц. Для значений K в пределах 1 ... 255 период T изменяется от 46 до 3871 мкс, а частота f соответственно от 21,739 к $\Gamma$ ц до 258,3  $\Gamma$ ц.

Значение K для заданного значения периода следования вычисляется по формуле K = [(T-31)/15], где T- период, мкс. Тогда для T=1000 мкс (f=1 к $\Gamma$ ц) получим  $K \approx 65$ . Истинное значение периода для такого параметра задержки будет  $T_{\text{ист}} = 1006$  мкс, а частота -994  $\Gamma$ ц, что в пределах  $\pm 1$  % от заданного значения.

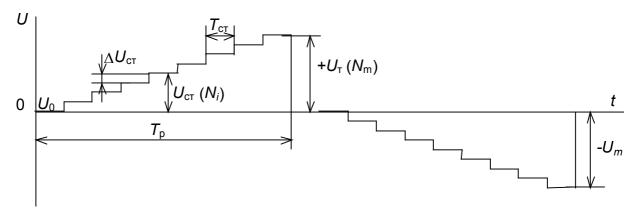

#### Пилообразное ступенчатое напряжение

Зададим для определенности параметры формируемого сигнала: длительность развертки  $T_{\rm p}=3$  мс; высота ступеньки  $|\Delta U_{\rm cr}|\leq 0,1$  В; амплитуда сигнала  $U_m=\pm 5$  В (рис. 17).

Если принять во внимание, что диапазон преобразуемых в ЦАП чисел

Puc. 17

(см. рис. 9) равен  $\pm 127d$  ( $\pm 7Fh$ ), то единичному приращению кода будет соответствовать  $|\Delta U_{\rm cr}| = 5{\rm B} \ / \ 127 \le 0,1$  В. Следовательно, для того чтобы шаг квантования не превышал 0,1 В, приращение кода  $\Delta N$  не должно быть бо-

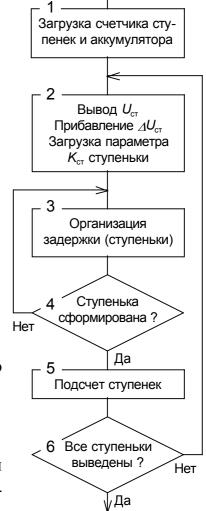

лее двух. При этом количество ступенек с учетом нулевого уровня сигнала будет равно  $N_{\rm cr} = N_{\it m}/\Delta N + 1$ . Блок-схема алгоритма формирования положительного участка сигнала приведена на рис. 18.

#### Программа формирования "пилы"

M0: mvib,Nm ;Инициализация счетчика mvia,0 ;ступенек (регистр B) и ;аккумулятора ( $U_0 = 0$ )

M1: out 0F4h ;(10) Вывод в порт A inr a ;(5) Приращение  $\Delta N$ =1 ;или ADI 02 ( $\Delta N$ =2) (7)

mvic,Кст ;(7)  $K_{cr}$  – задает длите-;льность ступеньки

M2: dcr c ;(5) Формирование jnz M2 ;(10) ступеньки cmp b ;(4) Формирование необ- jc M1 ;(10) ходимого числа ;ступенек

;Продолжение программы

Длительность ступеньки в тактах от одного вывода (команда OUT) до другого составляет

$$K_{\text{такт}} = 10 + 5 + 7 + (5 + 10) K_{\text{ст}} + 4 + 10 = 29 + (7 + 15K_{\text{ст}}).$$

Если полностью убрать задержку (операторы 3 и 4 см. рис. 18), то при этом реализуется максимальное быстродействие по выводу данных и будет сформирована минимальная по длительности ступенька напряжения:

$$K_{\text{такт}} = 29$$

,  $T_{\text{ст}} = 14,5$  мкс при  $f_0 = 2$  МГц.

Puc. 18

Длительность всей развертки  $T_{\rm p}$  в тактах составит  $K_{\rm p}=N_{\rm cr}\,K_{\rm такт}$  и одновременно  $K_{\rm p}=T_{\rm p}/\,T_0=6000$ . Задаваясь значением  $N_{\it m}=100$  ( $N_{\rm cr}=101$ ), получим  $K_{\rm такт}\cong 59$ , откуда  $15K_{\rm cr}+7=30$  не имеет целочисленного решения для  $K_{\rm cr}$ . В таком случае целесообразно заменить операторы 3 и 4, формирующие задержку, нескольким командами общей длительностью 30 тактов,

например MOV D, E шесть раз. Окончательно имеем  $0.5 \cdot 59 \cdot 101 = 2979$  мкс, что в пределах  $\pm 0.5$  % от  $T_p$ .

$T_{\text{рист}} =$

Приращение напряжения  $|\Delta U_{\rm cr}|$ , соответствующее  $\Delta N=1$  составит 5В / 100 = 50 мВ. Для ЦАП К572ПА1 опорное напряжение  $U_{\rm on}=10,24$  В, при этом вес младшего из 10 разрядов составляет 10,24В /  $2^{10}=10$  мВ. Если выводить кодовые выборки сигнала (семь информационных разрядов без учета знака) на старшие разряды ЦАП, то для младшего разряда выводимого кода вес составит 80 мВ ( $10 \text{ мВ} \cdot 2^3$ ). Для того чтобы получить требуемую величину 50 мВ, можно пропорционально уменьшить опорное напряжение до значения  $10,24 \cdot 50$  / 80=6,4 В.

Подобные изменения штатного опорного напряжения для ЦАП (АЦП) возможны далеко не всегда. Во всех случаях необходимо обращаться к справочной литературе [12, 13].

#### приложения

Приложение 1 Типовые исходные данные для МП КР580ВМ80 (по умолчанию)

| Данные                                   | PT-100 | PT-200 | PT-300 |

|------------------------------------------|--------|--------|--------|

| а) Тактовая частота микропроцессора, МГц | 2      | 1,6(6) | 1,3(3) |

| б) Период следования Т, мс               | 4      | 5      | 6      |

| в) Амплитуда сигнала $U$ , В             | 5      | 4      | 5      |

| г) Длительность импульсов $t_u$          | 0,1 T  | 0,1 T  | 0,1 T  |

| д) Шаг квантования                       |        |        |        |

| - по времени, не более мкс               | 50     | 60     | 70     |

| - по амплитуде, не болееВ                | 0,08   | 0,1    | 0,1    |

Приложение 2 Варианты заданий для курсовых работ

| №  | Тема                                       | Тип сигнала                                                | Дополнительные данные                    |

|----|--------------------------------------------|------------------------------------------------------------|------------------------------------------|

| 1  | Программируе-<br>мый генератор<br>сигналов | Синусоида,<br>непрерывный                                  | Предусмотреть задание начальной фазы 30° |

| 2  | >> >>                                      | "Пила", периодический биполярный +/- U                     | T T/2 T/2                                |

| 3  | >> >>                                      | >> >>                                                      | 0.9T 0.1T                                |

| 4  | >> >>                                      | >> >>                                                      | T/6 T/6 t                                |

| 5  | >> >>                                      | >> >>                                                      | T/2 t                                    |

| 6  | >> >>                                      | Синусоида, периодический импульсный                        | 0.3T t                                   |

| 7  | >> >>                                      | >> >>                                                      | T/6 t                                    |

| 8  | >> >>                                      | >> >>                                                      | T/3 t                                    |

| 9  | >> >>                                      | Равнобедренная трапе-<br>ция, периодический,<br>импульсный | T/6 T/3 t                                |

| 10 | >> >>                                      | Sin(x)/x, периодический, один боковой лепесток, биполярный | t                                        |

#### Продолжение таблицы

| No | Тема                                                         | Тип сигнала                                                                                               | Дополнительные<br>данные                       |

|----|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------|

| 11 | Программируемый генератор сигналов                           | Exp(-kx²), периодический, биполярный                                                                      | t                                              |

| 12 | >> >>                                                        | Парные биполярные импульсы, $t_{\pi} = t_{\mu}$                                                           | t <sub>n</sub> t <sub>u</sub> t <sub>n</sub> t |

| 13 | Измеритель длительно-<br>сти импульсов                       | Входной сигнал - уровни ТТЛ,<br>t <sub>и</sub> =1-10, 5-16, 10-20 мс для 1, 2,<br>3 групп, точность – 1 % | Предусмотреть индикацию результата             |

| 14 | Измеритель периода<br>следования импульсов                   | Входной сигнал - уровни ТТЛ,<br>Т =10-20, 25-50, 40-60 мс для 1,<br>2, 3 групп, точность – 1 %            | >> >>                                          |

| 15 | Вольтметр постоянного напряжения                             | Входное напряжение ± 5 В погрешности измерений =< 0,05 В период измерений Т                               | >> >>                                          |

| 16 | Вольтметр средних значений                                   | Входное напряжение ± 5 В погрешности измерений =< 0,05 В усреднение за 20 Т                               | >> >>                                          |

| 17 | Частотомер                                                   | Входной сигнал - "меандр" с уровнями ТТЛ, период $T \pm 0.3$ Т                                            | >> >>                                          |

| 18 | Программный счетчик числа событий (импульсов)                | Число каналов счета: 6, 8,12 для 1, 2, 3 групп. Входной сигнал-уровни ТТЛ                                 | >> >>                                          |

| 19 | Электронные часы на базе МПК (ОМЭВМ)                         | Начальная установка времени или установка по сигналам точного времени                                     | Индикация часов, минут (секунд)                |

| 20 | Программируемая линия задержки импульсной последовательности | Время задержки -20, 25, 30 мс для 1, 2, 3 групп. Выходной сигнал биполярный $(0=-U, 1=+U)$                | Один выход                                     |

| 21 | Устройство запоминания | Время запоминания - 1; 1,5; 2 | Воспроизвести запись |

|----|------------------------|-------------------------------|----------------------|

|    | аналогового сигнала    | секунды для 1, 2, 3 групп.    | по прерыванию        |

|    |                        | Объем ОЗУ=< 1 кбайт           |                      |

|    |                        |                               |                      |

#### Окончание таблицы

|    |                                                | <del>.</del>                                                                                                 | 0110111011101110111101111011110111101111                                              |

|----|------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| №  | Тема                                           | Тип сигнала                                                                                                  | Дополнительные<br>данные                                                              |

| 22 | Селектор импульсов по длительности             | Входные импульсы амплитудой 0,6 В, длительностью 30-500 мкс, интервал >=2 мс                                 | Селектируемые им-<br>пульсы >= 300 мкс,<br>выходные импульсы<br>ТТЛ, длительностью 1  |

| 23 | Селектор серий<br>импульсов                    | Входные импульсы амплитуды 0,8 В, длительность 50 мкс, интервал селекции 1 мс                                | <b>Се</b> лектируемая серия 8 импульсов, выходные импульсы ТТЛ, длительностью 200 мкс |

| 24 | Устройство для проверки ОЗУ емкостью 1 Кбайт   | Модуль ОЗУ на БИС<br>КР565РУ2; тестируемые сиг-<br>налы: 00h, 55h, Aah, FFh                                  | Индикация дефектных БИС и адреса дефектной ячейки                                     |

| 25 | Регулируемый генератор импульсов типа "меандр" | Диапазон Т = 100-2000, 200-<br>3000, 300-4000 мкс-1, 2, 3<br>групп с дискретом 20 мкс                        | Управляющий код регулировки задать аппаратно-наборным полем                           |

| 26 | Регулируемый генератор СПН ("пилы")            | Начальный уровень-0 В; высота ступеньки- 0,01В; крутизна В/мкс U/T – 0,1; 0,15; 0,2 –1,2,3 гр.               | Амплитуду U задать<br>аппаратно                                                       |

| 27 | Регулируемый генератор СПН ("пилы")            | См. условия варианта 26, высота ступеньки – 0,008 В, длительность обратного хода – 0,1 Т                     | >> >>                                                                                 |

| 28 | Регулируемый генератор СПН ("пилы")            | См. условия варианта 26, высота ступеньки – 0,008 В, длительность обратного хода = длительности прямого хода | >> >>                                                                                 |

| 29 | Цифровой фильтр-<br>дециматор                  | $y_n = \sum_{i=0}^{N-1} x_{n-i}$                                                                             | Предусмотреть инди-<br>кацию результата                                               |

|    |                                                |                                                                                                              |                                                                                       |

| 30 | Формирователь серий | Количество импульсов в      | Количество выходов |

|----|---------------------|-----------------------------|--------------------|

|    | импульсов           | серии программно варьирует- | от 2 до 4          |

|    |                     | ся от 2 до 10               |                    |

#### Рекомендательный библиографический список

- 1. Методические указания к лабораторным работам по дисциплинам микропроцессорного цикла. Ч.1 / Владим. гос. техн. ун-т; Сост. В.А. Егоров, А.И. Никитин.- Владимир, 1995.- 60 с.

- 2. *Калабеков Б.А.* Микропроцессоры и их применение в системах передачи и обработки сигналов.- М.: Радио и связь, 1988.- 368 с.

- 3. **Хвощ С.Т., Варлинский Н.Н., Попов Е.А.** Микропроцессоры и микро-ЭВМ в системах автоматического управления: Справ./ Под общ. ред. С.Т. Хвоща.- Л.: Машиностроение, 1987.- 640 с.

- 4. Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Справ. в 2 т./ В.Б. Абрайтис, Н.Н. Аверьянов, А.И. Белоус и др.; Под ред. В.А. Шахнова.- М.: Радио и связь, 1988.- Т.1, 368 с.

- 5. *Григорьев В.Л.* Программное обеспечение микропроцессорных систем.- М.: Энергоатомиздат, 1983.- 208 с.

- 6. *Балашов Е.П., Григорьев В.Л., Петров Г.А.* Микро- и миниЭВМ: Учеб. пособие для вузов.- Л.: Энергоатомиздат, 1984.- 376 с.

- 7. *Горбунов В.Л., Панфилов Д.И., Преснухин Д.Л.* Микропроцессоры. Основы построения микроЭВМ: Учеб. пособие для втузов. М.: Высш. шк., 1984.- 144 с.

- 8. *Гольденберг Л.М., Малев В.А., Малько Г.Б.* Цифровые устройства и микропроцессорные системы. Задачи и упражнения: Учеб. пособие для вузов.- М.: Радио и связь, 1992.- 256 с.

- 9. *Алексенко А.Г., Галицын А.А., Иванников А.Д.* Проектирование радиоэлектронной аппаратуры на микропроцессорах. Программирование, типовые решения, методы отладки.- М.: Радио и связь, 1984.- 272 с.

- 10. *Гришин Ю.П., Казаринов Ю.М., Катиков В.М.* Микропроцессоры в радиотехнических системах.- М.: Радио и связь, 1982- 236 с.

- 11. Полупроводниковые БИС запоминающих устройств: Справ./ В.В. Баранов и др.; Под ред. А.Ю. Гордонова и Ю.Н. Дьякова.- М.:Радио и связь, 1986.- 360 с.

- 12. **Федорков Б.Г., Телец В.А.** Микросхемы ЦАП и АЦП. Функционирование, параметры, применение.- М.: Энергоатомиздат, 1990.- 320 с.

- 13. *Лебедев О.Н.*, *Мирошниченко А.И.*, *Телец В.А.* Изделия электронной техники. Цифровые микросхемы. Микросхемы памяти. Микросхемы ЦАП и АЦП: Справ.- М.: Радио и связь, 1994.- 248 с.

- 14. Методические указания к лабораторным работам по дисциплинам микропроцессорного цикла. Ч.2 / Владим. гос. ун-т.; Сост.: В.А. Егоров, А.И. Никитин.- Владимир, 1997.- 32 с.

- 15. *Никитин А.И.*, *Никитин О.Р.* Микропроцессоры и микроЭВМ: Практикум / Владим. гос. ун-т.- Владимир,1998.- 128 с.

- 16. *Сташин В.В.*, *Урусов А.В.*, *Мологонцева О.Ф.* Проектирование цифровых устройств на однокристальных контроллерах.- М.: Энергоатомиздат, 1990.- 224 с.

- 17. Однокристальные микроЭВМ: Справ.- М.: МИКАП, 1994.- 400 с.

- 18. Микропроцессорные системы и микроЭВМ в измерительной технике: Учеб. пособие для вузов / А.Г. Филиппов, А.М. Аужбикович, В.М. Немчинов и др.- М.:Энергоатомиздат, 1995.- 368 с.

- 19. *Козаченко В.Ф.* Микроконтроллеры: руководство по применению 16-разрядных микроконтроллеров Intel MCS-196/296 во встроенных системах управления.- М.: ЭКОМ, 1997.- 688 с.

- 20. *Бродин В.Б., Шагурин И.И.* Микроконтроллеры. Архитектура, программирование, интерфейс. М.: ЭКОМ, 1999. 400 с.

- 21. *Пухальский Г.И.*, *Новосельцева Т.Я*. Проектирование дискретных устройств на интегральных микросхемах: Справ.-М.: Радио и связь, 1990.-304 с.

#### ОГЛАВЛЕНИЕ

|      | ВВЕДЕНИЕ                                         | 3  |

|------|--------------------------------------------------|----|

|      |                                                  |    |

|      | СПИСОК УСЛОВНЫХ СОКРАЩЕНИЙ                       | 4  |

| 1.   | ОБЩИЕ ВОПРОСЫ ПРОЕКТИРОВАНИЯ                     |    |

|      | МИКРОПРОЦЕССОРНЫХ УСТРОЙСТВ                      | 5  |

| 1.1. | Этапы проектирования микропроцессорных устройств | 6  |

| 1.2. | Проектирование основных блоков микропроцессорных |    |

|      | устройств                                        | 10 |

| 1.3. | Структурная схема микропроцессорной системы      | 18 |

| 1.4. | Разработка программного обеспече-                | 19 |

|      | ния                                              |    |

| 2. C | СОДЕРЖАНИЕ И ПОРЯДОК ВЫПОЛНЕНИЯ КУРСОВОГО        |    |

|      | ПРОЕКТА                                          | 21 |

|      | (РАБОТЫ)                                         |    |

| 2.1. | Содержание курсового проекта (работы)            | 22 |

| 2.2. | Порядок выполнения курсового проекта (работы)    | 22 |

| 2.3. | Оформление курсового проекта (работы)            | 23 |

| 3. ОСОБЕННОСТИ РАЗРАБОТКИ ПРОГРАММНО-АППАРАТНЫХ |    |

|-------------------------------------------------|----|

| СРЕДСТВ МИКРОПРОЦЕССОРНЫХ УСТРОЙСТВ             | 24 |

| 3.1. Аппаратная                                 | 24 |

| часть                                           |    |

| 3.2. Программная                                | 30 |

| часть                                           |    |

| ПРИЛОЖЕНИЯ                                      | 37 |

|                                                 |    |

| БИБЛИОГРАФИЧЕСКИЙ СПИСОК                        | 41 |

# МЕТОДИЧЕСКИЕ УКАЗАНИЯ К КУРСОВОМУ ПРОЕКТИРОВАНИЮ ПО ДИСЦИПЛИНАМ МИКРОПРОЦЕССОРНОГО ЦИКЛА

#### Составители НИКИТИН Александр Иванович ЕГОРОВ Валерий Александрович

Ответственный за выпуск – зав. кафедрой профессор О.Р. Никитин

Редактор Е.А. Амирсейидова Корректор В.В. Гурова Компьютерная верстка Е.Г. Радченко

ЛР № 020275. Подписано в печать 1.11.02 Формат 60х84/16. Бумага для множит. техники. Гарнитура Таймс. Печать офсетная. Усл. печ. л.2,09. Уч.-изд. л.2,22. Тираж 100 экз.

Заказ

Редакционно-издательский комплекс Владимирского государственного университета.

600000, Владимир, ул. Горького, 87.