Министерство образования Российской Федерации Владимирский государственный университет Кафедра управления и информатики в технических и экономических системах

# МЕТОДИЧЕСКИЕ УКАЗАНИЯ К ЛАБОРАТОРНЫМ РАБОТАМ ПО ДИСЦИПЛИНЕ «ВЫЧИСЛИТЕЛЬНЫЕ МАШИНЫ И СИСТЕМЫ»

Составители В.Г.Чернов В.П.Галас

УДК 621.3 (076.5)

Методические указания к лабораторным работам по дисциплине «Вычислительные машины и системы»/ В.Г.Чернов, В.П.Галас. Владимир, 2002. с.

Приведены описания лабораторных работ по дисциплине «Вычислительные машины и системы», в которых изучаются основные принципы построения современных вычислительных машин. Часть работ представляют собой программные модели, работа с которыми осуществляется в интерактивном режиме. Остальные работы выполнены в виде виртуальной электронной лаборатории на персональном компьютере с использованием пакета программ Electronic Workbench, позволяющего производить необходимые экспериментальные исследования.

Табл. Ил. Библиогр. назв.

### Лабораторная работа 1

## СИСТЕМЫ СЧИСЛЕНИЯ ПРАВИЛА ПЕРЕВОДА ЧИСЕЛ ИЗ ОДНОЙ СИСТЕМЫ СЧИСЛЕНИЯ В ДРУГУЮ

**Цель работы**. Изучение систем счисления, используемых в вычислительной технике и правил перевода чисел из одной системы счисления в другую.

При использовании ЭВМ существенным является знание систем счисления. Системы счисления, которыми мы пользуемся в настоящее время, основаны на методе, открытом индусскими математиками около 400 г. н.э. Арабы стали пользоваться подобной системой, известной как арабская система счисления около 800 г.н.э., а примерно в 1200 г.н.э. ее начали применять в Европе и называют десятичной системой счисления.

Известны другие системы счисления, основанные на тех же принципах, что и десятичная,- двоичная, восьмеричная и шестнадцатиричная. Они обычно используются в ЭВМ, поскольку вычислительные машины построены на схемах с двумя устойчивыми состояниями. В настоящей лабораторной работе предлагается изучить указанные системы счисления, а также методы преобразования чисел из одной системы счисления в другую.

### Описание лабораторной работы

Лабораторная работа представлена обучающей программой, работа с которой осуществляется в интерактивном режиме.

Запуск программы осуществляется из директории ЛабВМиС/Vmslab1, инициированием файла maindm.exe

Все действия, которые необходимо выполнить в ходе работы отражаются непосредственно на экране, либо их описания могут быть получены инициированием меню "Help".

### Содержание отчета

- 1. Краткое описание особенностей изученных систем счисления.

- 2.Результаты преобразования чисел из одной системы счисления в другую.

#### Вопросы для самопроверки

1. Чем отличаются позиционные системы счисления от непозиционных?

- 2.Как можно объяснить правила преобразования двоичной системы счисления в восьмеричную, шестнадцатиричную, двоично-десятичную и наоборот?

- 3.В каких случаях преобразование десятичной дроби в двоичную может быть выполнено за конечное число шагов и почему?

```

4.Переведите:

101101.101 2

в десятичную систему

47<sub>10</sub>

0.125_{10}

} в двоичную систему

24.375<sub>10</sub>

5.Переведите:

87.25<sub>10</sub>

} в восьмеричную систему;

1011.10 2

124.68

} в двоичную систему;

62.42<sub>8</sub>

6.Переведите:

BAD.DAD<sub>16</sub>

в десятичную систему;

374.971_{10}

} в шестнадцатиричную систему;

1011.101101<sub>2</sub>)

8AF.CB4<sub>16</sub>

в восьмеричную систему.

```

### Лабораторная работа 2

### ИЗУЧЕНИЕ ПРИНЦИПОВ ОРГАНИЗАЦИИ АРИФМЕТИКО-ЛОГИЧЕСКИХ УСТРОЙСТВ. СТРУКТУРА АЛУ ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ С ФИКСИРОВАННОЙ ЗАПЯТОЙ

**Цель работы:** Изучение принципов построения и функционирования АЛУ для сложения и вычитания чисел с фиксированной запятой.

### Краткие сведения из теории

Обычно в АЛУ операции алгебраического сложения сводятся к арифметическому сложению кодов чисел путем применения дополнительного или обратного кодов для представления отрицательных чисел.

Алгоритм выполнения в АЛУ арифметических операций зависит от того, в каком виде хранятся в памяти ЭВМ отрицательные числа в прямом или дополнительном. В последнем случае сокращается время выполнения операции за счет исключения операции преобразования получаемого в АЛУ дополнительного кода отрицательного результата в прямой код.

Алгоритм алгебраического сложения двоичных чисел с фиксированной запятой при использовании дополнительного кода для представления отрицательных чисел.

При выполнении операции сложения положительные слагаемые представляются в прямом коде, а отрицательные - в дополнительном. Производится сложение двоичных кодов, включая разряды знаков. Если при этом возникает перенос из знакового разряда суммы при отсутствии переноса в этот разряд или перенос в знаковый разряд при отсутствии переноса из разряда знака, то имеется переполнение разрядной сетки соответственно при отрицательной и положительной суммах. Если нет переносов из знакового разряда и в знаковый разряд суммы или есть оба эти переноса, то переполнения нет и при нуле в знаковом разряде сумма положительна и представлена в прямом коде, а при 1 в знаковом разряде сумма отрицательна и представлена в дополнительном коде.

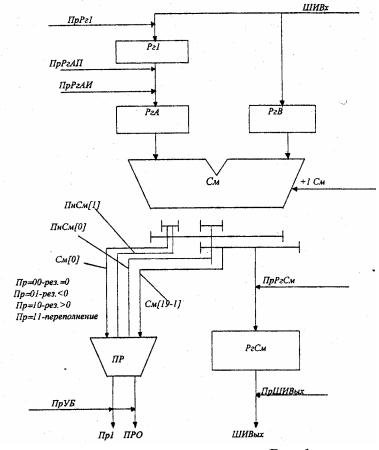

Упрощенная структурная схема АЛУ для операций сложения и п-разрядных (n-й знаковый) двоичных вычитания разряд чисел  $\mathbf{c}$ фиксированной Предполагается, запятой приведена на рис.1. что отрицательные числа хранятся в памяти в дополнительном коде.

В состав АЛУ входят п-разрядный параллельный комбинационный сумматор См, регистр сумматора PrCм, входные регистры сумматора PrB и PrA, входной регистр АЛУ Pr1.

Рис.1

Из оперативной памяти по входной информационной шине ШИвк в АЛУ поступают операнды: положительные числа в прямом коде, а отрицательные в дополнительном. Операнды размещаются в PrB (первое слагаемое или уменьшаемое) и Pr1 (второе слагаемое или вычитаемое); Pr1 связан с PrA цепями прямой и инверсной передачи кода. Результат операции выдается из АЛУ в оперативную память по выходной информационной шине ШИвых. Запись информации в регистры АЛУ осуществляется под управлением сигналов ПрРr1 и ПрPrB. Слово из Pr1 в PrA передается в прямом коде под действием управляющего сигнала ПрPrAП, в инверсном коде ПрPrAИ. Сигнал ПрPrСм управляет записью результата в регистр сумматора PrCM, а сигнал ПрИШвых - передачей содержимого PrCM в информационную шину.

При выполнении операции в АЛУ помимо результата операции формируется 2-х разрядный код признака результата ПР, который принимает следующие значения:

| Результат операции | Признак р | езультата |

|--------------------|-----------|-----------|

| =0                 | 0         | 0         |

| < 0                | 0         | 1         |

Код признака результата формируется комбинационной схемой Пр, на выходы которой поступают выходные сигналя всех разрядов сумматора СМ, а также сигналы переноса из знакового разряда ПнСМ[0] и из старшего цифрового разряда ПнСМ[1].

Признак переполнения (ПР=11) формируется, если выполняется условие

(1)  $\Pi$ нСМ[0] $\land \Pi$ нСМ[1] $\lor \Pi$ нСМ[0] $\land \Pi$ нСМ[1]=1

Признак нулевого значения результата Пр=00 формируется если

$$\begin{array}{c} \text{n-1} \\ \text{(2)} \land \overline{CM[i]} = 1 \\ \text{i=0} \end{array}$$

Признак положительного результата Пр=10 формируется при условии

- (3)  $\overline{\text{CM[0]}}(\Pi\text{HCM[0]}\backslash\Pi\text{HCM[1]}\backslash\overline{\Pi\text{HCM[0]}}\backslash\overline{\Pi\text{HCM[1]}}=1$  отрицательного результата  $\Pi\text{p=01}$  при условии

- (4) CM[0]( $\Pi$ HCM[0]/ $\Pi$ HCM[1]/ $\overline{\Pi$ HCM[0]/ $\overline{\Pi}$ HCM[1]

При выполнении алгебраического сложения поступившие в АЛУ коды операндов находятся в выходных регистрах PrB и PrA сумматора. Код суммы формируется на выходе схемы См и фиксируется в регистре PrCм.

Операция алгебраического вычитания

$$Z=X-Y=X+(-Y)$$

может быть сведена к изменению знака вычитаемого Y и операции алгебраического сложения. Изменению знака соответствует следующая процедура: принятый в Pr1 код числа знака передается инверсно в PrA и при сложении осуществляется подсуммирование 1 в младший разряд сумматора.

### Выполнение лабораторной работы.

Структуры АЛУ для сложения и вычитания чисел с фиксированной запятой и алгоритм его функционирования моделируется с помощью программы, реализованной на языке Турбо-Паскаль.

Работа с программой осуществляется в интерактивном режиме. После запуска файла summator.exe в директории ЛабВМиС/Vmslab2 на экране

дисплея появляется инструкция для пользователя, согласно которой и выполняется лабораторная работа.

Выполнение изучаемой операции АЛУ осуществляется по шагам и результат каждого шага отражается на экране в виде кодов содержимого соответствующих регистров, промежуточных и конечных результатов.

В процессе выполнения лабораторной работы необходимо изучить работу Алу в следующих режимах:

- -сложение двух положительных чисел без возникновения переполнения;

- сложение двух положительных чисел с возникновением переполнения;

- сложение двух отрицательных чисел без возникновения переполнения

- сложение двух отрицательных чисел с возникновением переполнения

- вычитание x-y , x>y;

- вычитание x-y , x<y;

- вычитание x-y, x=y;

Для всех режимов зафиксировать по шагам состояния всех элементов АЛУ, индицируемые соответствующими кодами,а также состояния управляющих сигналов. Для всех режимов привести последовательность формирования признаков результата.

По результата работы необходимо построить блок-схему микропрограммы работы АЛУ, а также выполнить синтез комбинационной схемы, формирующей признаки результата.

### Содержание отчета.

- 1. Описание работы АЛУ.

- 2. Блок-схема микропрограммы выполнения операций сложения (вычитания) для чисел с фиксированной запятой.

- 3. Логические уравнения, по которым выполнялся синтез комбинационной схемы формирования признаков результата, а также ее схему.

### Вопросы для самопроверки

- 1.Сколько вариантов имеет представление нуля в обратном коде?

- 2. Когда используется прямая или инверсная передача кодов из входного регистра АЛУ?

- 3. Для какой цели в сумматоре используется вход подсуммирования "1" в младший разряд?

- 4. Самостоятельно подберите пары слагаемых при которых:

- возникает переполнение при положительной сумме;

- переполнение при отрицательной сумме;

- результат отрицательный;

- результат положительный;

Докажите, что признаки формируются в соответствии с условиями (1-4).

- 5. Какие операции при выполнении сложения (вычитания) влияют на скорость их выполнения?

- 6. Что такое перенос и как он формируется?

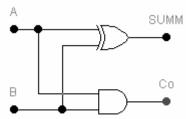

- 7. Нарисуйте схему полусумматора.

- 8. Нарисуйте схему полного сумматора.

- 9.В чем различия между полусумматором и полным сумматором?

- 10. Чем отличаются операции суммирования для чисел с фиксированной и плавающей запятой?

### Лабораторная работа №3

### Исследование схем сумматоров

### Цель работы

- 1. Синтез схем сумматоров различного типа.

- 2. Исследование внутренней структуры и логики функционирования сумматоров.

#### Приборы и элементы

Логический преобразователь Логический анализатор Генератор слов Цифровой индикатор Источник напряжения + 5 В

#### Краткие сведения из теории

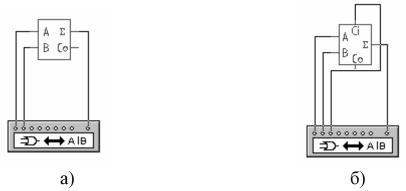

Арифметические сумматоры являются составной частью так называемый арифметико-логических устройств (АЛУ) микропроцессоров (МП). Они используются также для формирования физического адреса ячеек памяти в МП с сегментной организацией памяти. В программе EWB арифметические сумматоры представлены в библиотеке двумя базовыми устройствами, показанными на рис. 1: полусумматором (а) и полным сумматором (б).

Рис.1 Схемы полусумматора (а) и полного сумматора (б)

Они имеют следующие назначения выводов: A, B — входы слагаемых,  $\sum$  — результат суммирования. Со — выход переноса, Ci — вход переноса.

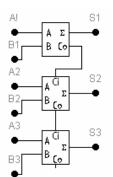

Многоразрядный сумматор создается на базе одного полусумматора и n

полных сумматоров. В качестве примера на рис. 2 приведена структура трехразрядного сумматора. На входы Al, A2, A3 и B1, B2, B3 подаются первое и второе слагаемые, соответственно, а с выходов SI, S2, S3 снимается результат суммирования.

Рис. 2. Трехразрядный сумматор

Для исследования внутренней структуры и логики функционирования сумматоров как нельзя лучше подходит логический преобразователь. После подключения полусумматора к преобразователю согласно рис. 3*а* последова-

101

тельно нажимаем кнопки толучаем таблицу истинности и булево выражение.

Рис.3 Схемы подключения полусумматора (a) и полного сумматора (б) к логическому преобразователю

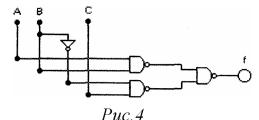

Изучив полученные данные, приходим к выводу, что при подключении вывода полусумматора к зажиму ОUТ преобразователя (как показано на рис. 3а) он выполняет функции элемента Исключающее ИЛИ. Подключив клемму ОUТ преобразователя к выходу Со полусумматора и проделав аналогичные действия, приходим к выводу, что в таком включении полусумматор выполняет функции элемента И. Следовательно, эквивалентная схема полусумматора имеет вид, показанный на рис.4.

Рис. 4. Структура библиотечного полусумматора

В каталоге программы EWB 5.12 имеется схема включения четырехразрядного АЛУ (файл alu'l81.ewb) на базе серийной микросхемы 74181 (отечественный аналог К155ИПЗ).

Значения четырехразрядных операндов A и B на входе задаются с помощью генератора слова и в шестнадцатеричном коде отображаются одноименными алфавитно-цифровыми индикаторами. На выходах FO.. .F3 результат

суммирования отображается индикатором F. Изменяя состояния сигналов на управляющих входах, можно промоделировать большинство функций АЛУ, используемых в микропроцессорах.

## Порядок проведения экспериментов Эксперимент 1. Исследование логики функционирования полусумматора.

Подключите полусумматор к логическому преобразователю в соответствии со схемой, изображенной на рис.3а. Получите таблицу истинности и булево выражение исследуемого элемента. Переключите клемму ОUТ преобразователя к выходу Со полусумматора и проделайте аналогичные действия. Убедитесь что в таком включении полусумматор выполняет функции элемента И. Заполните соответствующие таблицы в разделе "Результаты экспериментов".

### Эксперимент 2. Исследование логики функционирования полного сумматора.

Подключите полный сумматор к логическому преобразователю в соответствии со схемой, изображенной на рис.3б. Выясните внутреннюю структуру полного сумматора, пользуясь схемой его подключения к логическому преобразователю и принимая во внимание методику решения аналогичной задачи для полусумматора. Заполните соответствующие таблицы в разделе "Результаты экспериментов".

### Эксперимент 3. Исследование логики функционирования трехразрядного сумматора.

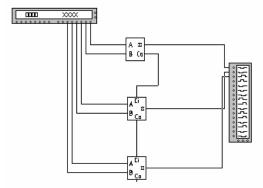

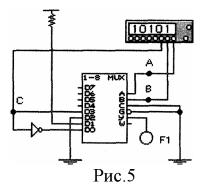

Подключите входы трехразрядного сумматора к соответствующим клеммам генератора слова, а выходы к логическому анализатору в соответствии со схемой, изображенной на рис.5.

Рис.5 Схема подключения трехразрядного сумматора

Для удобства проведения экспериментов рекомендуется при установке режима работы генератора слова установить частоту (Frequency) 1Гц и, после нажатия кнопки *Pattern*, выбрать опцию *Up Counter*. Эту же

частоту рекомендуется использовать и в логическом анализаторе, установив ее после нажатия кнопки *Clock Set* трехразрядного сумматора. Зарисуйте осциллограммы с его выходов и поместите в раздел "Результаты экспериментов".

### Эксперимент 4. Исследование логики функционирования четырехразрядного АЛУ на базе серийной микросхемы 74181.

Откройте файл alu'181.ewb. Проверьте правильность функционирования четырехразрядного АЛУ. Проверьте работу ИМС 74181 в режиме сумматора с переносом (на вход CN подайте сигнал логического нуля).

Зарисуйте осциллограммы с выходов АЛУ и поместите в раздел "Результаты экспериментов".

### Результаты экспериментов

### Эксперимент 1. Исследование логики функционирования полусумматора.

Таблица истинности

| 1 4 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |       |        |   |

|-----------------------------------------|-------|--------|---|

| входы                                   |       | выходы |   |

| $a_i$                                   | $b_i$ | S      | p |

|                                         |       |        |   |

|                                         |       |        |   |

|                                         |       |        |   |

|                                         |       |        |   |

| Булево выражение |  |

|------------------|--|

|                  |  |

|                  |  |

Эксперимент 2. Исследование логики функционирования полного сумматора.

|           | истинност      |                       |         |              |                           |              |               |        |

|-----------|----------------|-----------------------|---------|--------------|---------------------------|--------------|---------------|--------|

|           |                |                       |         |              |                           |              |               |        |

|           |                |                       |         |              |                           |              |               |        |

|           |                |                       |         |              |                           |              |               |        |

|           |                |                       |         |              |                           |              |               |        |

|           |                |                       |         |              |                           |              |               |        |

|           |                |                       |         |              |                           |              |               |        |

|           |                |                       |         |              |                           |              |               |        |

|           |                |                       |         |              |                           |              |               |        |

|           |                |                       |         |              |                           |              |               |        |

|           |                | <u> </u>              |         |              |                           |              |               |        |

| Булево вы | <i>аражени</i> | e                     |         |              |                           |              |               |        |

|           |                |                       |         |              |                           |              |               |        |

|           |                |                       |         |              |                           |              |               |        |

| Экспери   | мент 3. И      | сследова              | ние лог | ики фу       | нкци                      | онир         | ован          | ия тре |

| рядного   |                |                       |         |              |                           |              |               |        |

| ридного:  | Cymmaiup       | <i>,</i>              |         |              |                           |              |               |        |

| ридного   | Сумматор       | ,                     |         |              |                           |              |               |        |

| ридного   | Сумматор       | ,                     |         |              |                           |              |               |        |

| ридного   | сумматор       |                       |         |              |                           |              |               |        |

| ридного   | Сумматор       |                       |         |              |                           |              |               |        |

| ридного   |                | , <b></b>             |         |              |                           |              |               |        |

| ридного   |                |                       |         |              |                           |              |               |        |

| ридного   |                |                       |         |              |                           |              |               |        |

| ридного   | Сумматор       |                       |         |              |                           |              |               |        |

|           |                |                       | ние лог | ики фу       | ткци                      | онир         | ован          | ия чет |

| Экспери   | мент 4. И      | сследова<br>на базе с | ние лог | ики фу       | тнкци(                    | онир<br>ы 74 | ован<br>181.  | ия чет |

| Экспери   | мент 4. И      | сследова              | ние лог | ики фу       | тнкцис                    | онир<br>ы 74 | овані<br>181. | ия чет |

| Экспери   | мент 4. И      | сследова              | ние лог | ики фу       | ткци(<br>осхем)           | онир<br>ы 74 | ован<br>181.  | ия чет |

| Экспери   | мент 4. И      | сследова              | ние лог | ики фуй микр | т <b>нкци</b> (<br>осхем) | онир<br>ы 74 | ован<br>181.  | ия чет |

| Экспери   | мент 4. И      | сследова              | ние лог | ики фу       | тнкцио                    | онир<br>ы 74 | ован<br>181.  | ия чет |

| Экспери   | мент 4. И      | сследова              | ние лог | ики фу       | ткци(<br>осхем)           | онир<br>ы 74 | ован<br>181.  | ия чет |

| Экспери   | мент 4. И      | сследова              | ние лог | ики фу       | т <b>нкци</b> (           | онир<br>ы 74 | овані<br>181. | ия чет |

| Экспери   | мент 4. И      | сследова              | ние лог | ики фу       | тнкцио                    | онир<br>ы 74 | овані<br>181. | ия чет |

### Лабораторная работа №4

### Синтез и исследование логических схем

#### Цель работы

- 1. Исследование логических схем.

- 2. Реализация логических функций при помощи логических элементов.

- 3. Синтез логических схем, выполняющих заданные логические функции.

#### Приборы и элементы

Логический преобразователь

Генератор слов

Вольтметр

Логические пробники

Источник напряжения + 5 В

Источник сигнала "логическая единица"

Двухпозиционные переключатели

Двухвходовые элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ

Микросхемы серии 74.

### Краткие сведения из теории

Логические элементы это устройства реализующие одну из операций алгебры логики или простейшую логическую функцию. Схема, составленная из конечного числа логических элементов по определенным правилам, называется логической схемой.

Основным логическим функциям соответстввуют выполняющие их схемные элементы.

Так как область определения любой функции п переменных конечна ( $2^n$  значений), такая функция может быть задана таблицей значений  $f(v_i)$ , которые она принимает в точках  $v_i$ , где  $i=0,1\dots 2^n-1$ . Такие таблицы называют таблицами истинности. В таблице 1 представлены таблицы истинности, задающие функции конъюнкции (f1), дизъюнкции (f2), конъюнкции с инверсией (f3), дизъюнкции с инверсией (f4), суммировавния по модулю 2 (f5), равнозначности (f6).

Таблица 1

| i |   | іение<br>іенных |    |    | фуні | кция |    |    |

|---|---|-----------------|----|----|------|------|----|----|

|   | X | у               | f1 | f2 | f3   | f4   | f5 | f6 |

| 0 | 0 | 0               | 0  | 0  | 1    | 1    | 0  | 1  |

| 1 | 0 | 1               | 0  | 1  | 1    | 0    | 1  | 0  |

| 2 | 1 | 0               | 0  | 1  | 1    | 0    | 1  | 0  |

| 3 | 1 | 1               | 1  | 1  | 0    | 0    | 0  | 1  |

i=2x+y - число, образованное значениями переменных.

### Порядок проведения экспериментов

### Эксперимент 1. Исследование логической функции И.

### а). Задание уровней логических сигналов.

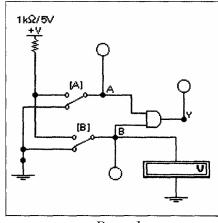

Откройте в Electronics Workbench файл c12\_01 со схемой, изображенной на рис. 1. В этой схеме два двухпозиционных переключателя A и В подают на входы логической схемы И уровни 0 (контакт переключателя в нижнем поло-

жении) или 1 (контакт переключателя в верхнем положении). Включите схему. Установите переключатель В в нижнее положение. Измерьте вольтметром напряжение на входе В и определите с помощью логического пробника уровень логического сигнала. Установите переключатель В в верхнее положение. Определите уровень логического сигнала и запишите показания вольтметра; укажите, какой логический сигнал формируется на выходе Y. Результаты занесите в раздел "Результаты экспериментов".

Puc. 1

### б). Экспериментальное получение таблииы, истинности элемента И.

Подайте на входы схемы все возможные комбинации уровней сигналов А и В и для каждой комбинации зафиксируйте уровень выходного сигнала Y. Заполните таблицу истинности логической схемы И (табл. I в разделе "Результаты экспериментов").

### в). Получение аналитического выражения для функции.

По таблице 1 составьте аналитическое выражение функции элемента И и занесите его в раздел "Результаты экспериментов".

### Эксперимент 2. Исследование логической функции ИЛИ.

### а). Экспериментальное получение таблицы истинности логического элемента ИЛИ.

Соберите схему *рис.* 2. Включите схему. Подайте на входы схемы все возможные комбинации уровней входных сигналов и, наблюдая уровни сигналов на входах и выходе с помощью логических пробников, заполните таблицу истинности логической схемы ИЛИ *(табл. 2 в разделе "Pe-тинности разделе "ре-тинности разделе"*

Puc. 2

зультаты экспериментов").

**б).** Получение аналитического выражения для функции. По таблице 2 составьте аналитическое выражение функции и занесите его в раздел "Результаты экспериментов".

### Эксперимент 3. Исследование логических схем с помощью генератора слов.

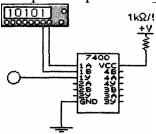

а). Сведения об исследуемой микросхеме.

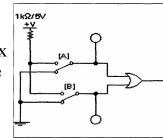

Откройте файл c12 02 со схемой, изображенной на рис. 3.

Puc. 3

Включите схему. Укажите, к каким выводам микросхемы 7400 подключается источник питания, сколько элементов 2И-НЕ содержит микросхема, сколько элементов используется в данном эксперименте и как обозначены на схеме используемые входы и выходы. Заполните таблицу сведений о микросхеме (табл. 3 в разделе "Результаты экспериментов").

*б).* Экспериментальное получение таблицы истинности логического элемента 2*И*-НЕ. Запрограммируйте генератор слов так, чтобы на выходе генератора получать последовательно следующие комбинации: 00, 01, 10, 11. Переведите генератор в режим пошаговой работы нажатием кнопки "Step" на увеличенном изображении генератора. Каждое нажатие кнопки "Step" вызывает переход к очередному слову заданной последовательности, которое подается на выход генератора. Последовательно подавая на микросхему слова из заданной последовательности, заполните таблицу истинности элемента 2*И*-НЕ (табл. 4 в разделе "Результаты экспериментов").

^ Указание: значения разрядов текущего слова на выходе генератора отображаются в круглых окнах в нижней части на панели генератора.

### Эксперимент 4. Реализация логической функции 3-х переменных.

а). Синтез схемы, реализующей функцию, заданную логическим выражением.

Реализуйте функцию f = ab v be на элементах 2И-НЕ.

Указание. Представьте выражение функции через операции логического

умножения и инверсии.

Соберите в Electronics Workbench схему на элементах 2И-НЕ, соответствующую полученному выражению. Подключите к входам схемы генератор слов, к выходу – логический пробник. Генератор слов запрограммируйте на формирование последовательности из восьми слов, соответствующих числам от 0 до 7: 0=000; 1=001; 2=010; 3=011; 4=100; 5=101; 6=110; 7=111. В пошаговом режиме, последовательно подавая на вход полученной схемы все слова последовательности, определите при помощи логического пробника уровень сигнала на выходе схемы. По полученным результатам заполните таблицу 5 в разделе "Результаты экспериментов".

### б). Синтез схемы, реализующей заданную функцию при помощи логического преобразователя.

Для получения схемы, реализующей функцию, описываемую логическим выражением  $f=ab\ v\ bc$ , можно воспользоваться логическим преобразователем. Для этого проделайте следующее:

- вызовите логический преобразователь;

- введите в нижнее окно панели преобразователя логическое выражение ab v bc с клавиатуры (операции ИЛИ соответствует знак +, инверсия обозначается апострофом);

- для реализации схемы на элементах И-НЕ нажмите клавишу  $A|B \longrightarrow NAND$  на панели логического преобразователя.

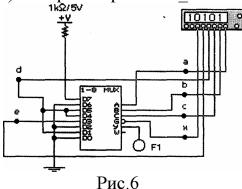

Логический преобразователь выводит на рабочее поле схему, реализующую функцию, описываемую введенным логическим выражением. Полученная схема приведена на рис. 4. К схеме подключите генератор слов, запрограммированный на формирование восьми слов, соответствующих числам от 0 до 7: 0=000; 1=001; 2=010; 3=011; 4=100; 5=101; 6=110; 7=111.

Переведите генератор слов в пошаговый режим. Включите схему. Последова-

тельно подавая на входы схемы указанные слова и определяя уровень сигнала на выходе схемы логическим пробником, заполните таблицу истинности (табл. 6 в разделе "Результаты экспериментов"). Вычислите промежу-

точные значения и занесите их в таблицу истинности

(табл. 6 в разделе "Результаты экспериментов"). Они определяют логические сигналы на входе третьего элемента 2И-НЕ в схеме (для контроля результатов вычисления можно к его входам подключить логические пробники).

### Результаты экспериментов

### Эксперимент 1. Исследование логической функции И.

| ١              | 7              | ~        |             |           |

|----------------|----------------|----------|-------------|-----------|

| $\alpha$       | <i>Kanauuo</i> | VNARHOU  | логических  | СПЗНАПОВ  |

| $\alpha_{I}$ . | Judunuc        | ypoonen. | noch accrus | cachanoo. |

| Напряжение на входе В (ключ В в нижнем положении),        | _B |

|-----------------------------------------------------------|----|

| Логический сигнал на входе В (ключ В в нижнем положении)  |    |

| Напряжение на входе В (ключ В в верхнем положнии),        | E  |

| Логический сигнал на входе В (ключ В в верхнем положении) |    |

| Логический сигнал на выходе Ү                             |    |

### $\delta$ ). Экспериментальное получение таблицы истинности элемента $\emph{\textbf{\textit{U}}}.$

Таблица 1

| Входы |   | Выход |

|-------|---|-------|

| A     | В | Y     |

| 0     | 0 |       |

| 0     | 1 |       |

| 1     | 0 |       |

| 1     | 1 |       |

| <i>6</i> ). | Получени | е аналитического | выражения | для с | функции. |

|-------------|----------|------------------|-----------|-------|----------|

|-------------|----------|------------------|-----------|-------|----------|

| Аналитическое выражение для функции |  |

|-------------------------------------|--|

### Эксперимент 2. Исследование логической функции ИЛИ.

### а). Экспериментальное получение таблицы истинности логического элемента ИЛИ.

Таблица 2

| Входы |   | Выход |

|-------|---|-------|

| A     | В | Y     |

| 0     | 0 |       |

| 0     | 1 |       |

| 1     | 0 |       |

| 1     | 1 |       |

### в). Получение аналитического выражения для функции.

Аналитическое выражение для функции

Эксперимент 3. Исследование логических схем с помощью генератора слов.

### а). Сведения об исследуемой микросхеме.

Таблица 3

| Число элементов И-НЕ в микросхеме                     |  |

|-------------------------------------------------------|--|

| Число исследуемых элементов 2И-НЕ                     |  |

| Обозначение выводов для подключения источника питания |  |

| Обозначения используемых входов                       |  |

| Обозначение используемого выхода                      |  |

### б). Экспериментальное получение таблицы истинности логического элемента 2И-НЕ микросхемы, 7400.

Таблица 4

| Входы |   | Выход |

|-------|---|-------|

| A     | В | Y     |

| 0     | 0 |       |

| 0     | 1 |       |

| 1     | 0 |       |

| 1     | 1 |       |

### Эксперимент 4. Реализация логической функции 3-х переменных.

### а). Синтез схемы, реализующей функцию, заданную логическим выражением.

Аналитическое выражение для функции f в базисе И-НЕ

Схемная реализация

Таблица 5

| a | Ъ | С | f |

|---|---|---|---|

| 0 | 0 | 0 |   |

| 0 | 0 | 1 |   |

| 0 | 1 | O |   |

| 0 | 1 | 1 |  |

|---|---|---|--|

| 1 | 0 | 0 |  |

| 1 | 0 | 1 |  |

| 1 | 1 | О |  |

| 1 | 1 | 1 |  |

### б). Синтез схемы, реализующей заданную функцию при помощи логического преобразователя.

Таблица 6.

| 140 | nuga 0. |   |    |     |   |

|-----|---------|---|----|-----|---|

| a   | b       | c | ab | ¯ c | f |

| 0   | 0       | 0 |    |     |   |

| 0   | 0       | 1 |    |     |   |

| 0   | 1       | 0 |    |     |   |

| 0   | 1       | 1 |    |     |   |

| 1   | 0       | 0 |    |     |   |

| 1   | 0       | 1 |    |     |   |

| 1   | 1       | 0 |    |     |   |

| 1   | 1       | 1 |    |     |   |

### Вопросы

- 1. Что такое логическая переменная и логический сигнал? Какие значения они могут принимать?

- 2. Что такое логическая функция?

- 3. Может ли быть логическим сигналом уровень напряжения? Состояние контакта? Свечение светодиода?

- 4. Какая логическая функция описывает поведение системы пуска трехфазного двигателя (двигатель может быть запущен, если три датчика подтверждают наличие фазных напряжений)?

- 5. Датчик температуры состоит из контакта, который замыкается (размыкается) при превышении температуры. При замыкании контакта вырабатывается сигнал логической единицы, при размыкании логического нуля. Какую схему следует использовать для обнаружения срабатывания хотя бы одного датчика пожарной сигнализации?

- а) при повышении температуры в датчике происходит замыкание контакта;

- б) при повышении температуры в датчике происходит размыкание контакта.

- 6. Какой сигнал должен быть подан на неиспользуемые входы элемента 8И-НЕ, если требуется реализовать функцию 5И-НЕ?

- 7. Какой сигнал должен быть подан на неиспользуемый вход элемента 4ИЛИ-НЕ при реализации функции ЗИЛИ-НЕ?

- 8. В вашем распоряжении имеются логические элементы 2И-НЕ. Как на их основе сделать схему ЗИ? Достаточно ли 4-х элементов 2И-НЕ для выполнения этой задачи?

- 9. Как будет вести себя схема И, если на одном из входов вследствие внутренней неисправности будет постоянно присутствовать логическая единица? Логический нуль? Составьте таблицу истинности для неисправной схемы ЗИ. Определите поведение схемы И-НЕ при тех же условиях.

- 10. Как будет вести себя схема ИЛИ, если на одном из входов вследствие внутренней неисправности будет постоянно присутствовать логическая единица? Логический нуль? Составьте таблицу истинности для неисправностей схемы ЗИЛИ. Определите поведение схемы ИЛИ-НЕ при тех же условиях.

### Лабораторная работа №5

### Исследование комбинационных схем средней степени интеграции

**Комбинационной схемой** называется логическая схема, реализующая однозначное соответствие между значениями входных и выходных сигналов. Для реализации комбинационных схем используются логические элементы, выпускаемые в виде интегральных схем. В этот класс входят интегральные схемы дешифраторов, -шифраторов, мультиплексоров, демультиплексоров, сумматоров.

### 5.1. Исследование дешифраторов

### Цель работы

- 1. Ознакомление с принципом работы дешифраторов.

- 2. Исследование влияния управляющих сигналов на работу дешифраторов.

- 3. Реализация и исследование функциональных модулей на основе дешифраторов.

#### Приборы и элементы

Логический преобразователь

Генератор слов

Вольтметр

Логические пробники

Источник напряжения + 5 В

Генератор слов

Генератор тактовых импульсов

Двухпозиционные переключатели

Демультиплексор

Источник сигнала "логическая единица"

Логические пробники

Микросхема 74138 - дешифратор 3х8

### Краткие сведения из теории

**Дешифраторы** - это комбинационные схемы с n входами и  $m=2^n$  выходами. Единичный сигнал, формирующийся на одном из m выходов, однозначно соответствует комбинации входных сигналов. Обычно входы управления используются для каскадирования (увеличения разрядности) дешифраторов или при параллельной работе нескольких схем на общие выходные линии.

Дешифратор может быть использован и как демультиплексор — логический коммутатор, подключающий входной сигнал к одному из выходов. В этом случае функцию информационного входа выполняет один из входов разрешения, а состояние входов С, В и А задает номер выхода, на который передается сигнал со входа разрешения.

Дешифраторы широко используются в ЭВМ для выбора информации по определенному адресу, для расшифровки кода операции и др.

**Шифратор** решает задачу, обратную схемам дешифраторов, т. е. по номеру входного сигнала формирует однозначную комбинацию выходных сигналов.

### Порядок проведения экспериментов

Эксперимент 1. Исследование принципа работы дешифратора 3х8 в основном режиме.

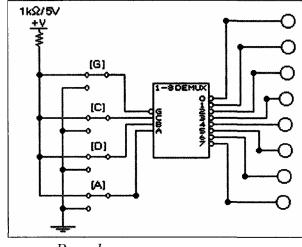

Откройте файл с13 01 со схемой, изображенной на рис. 1. Включите

схему. Подайте на вход G уровень логической единицы. Для этого клавишей G ключ G установить в верхнее положение. Определите и запишите уровни сигналов на выходах YO...Y7 в таблицу истинности при G = 1 (табл. I в разделе "Результаты экспериментов").

Подайте на вход G уровень логического нуля (ключ G установите в нижнее положение). Убедитесь, что дешифратор перешел в рабочий режим и на одном из

*Puc.* 1

выходов установился уровень логического нуля. Подавая все возможные комбинации уровней логических сигналов на входы A, B, C с помощью одноименных ключей и определяя с помощью логических пробников уровни логических сигналов на выходе схемы, заполните таблицу истинности дешифратора при G=0 (табл. 1. в разделе "Результаты экспериментов").

### Результаты экспериментов Эксперимент 1. Исследование работы дешифратора 3x8 в основном режиме.

| I | 'аблица | 1 |

|---|---------|---|

|   |         |   |

| C | В | A | G | YO | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 |

|---|---|---|---|----|----|----|----|----|----|----|----|

| 0 | 0 | 0 | 1 |    |    |    |    |    |    |    |    |

| 0 | 1 | 1 | 1 |    |    |    |    |    |    |    |    |

| 0 | 0 | 1 | 0 |    |    |    |    |    |    |    |    |

| 0 | 1 | 0 | 0 |    |    |    |    |    |    |    |    |

| 0 | 1 | 1 | 0 |    |    |    |    |    |    |    |    |

| 1 | 0 | 0 | 0 |    |    |    |    |    |    |    |    |

| 1 | 0 | 1 | 0 |    |    |    |    |    |    |    |    |

| 1 | 1 | 0 | 0 |    |    |    |    |    |    |    |    |

| 1 | 1 | 1 | 0 |    |    |    |    |    |    |    |    |

<sup>^</sup> Для простоты заполнения таблицы истинности в ней можно отмечать только выводы с низким уровнем сигнала.

### **5.2.** Исследование мультиплексоров Цель работы

- 1. Ознакомление с принципом работы мультиплексора.

- 2. Реализация и исследование функциональных модулей на основе мультиплексоров.

### Приборы и элементы

Генератор слов

Генератор тактовых импульсов

Двухпозиционные переключатели

Источник напряжения + 5 В

Источник сигнала "логическая единица"

Логические пробники

Мультиплексор

Микросхема 74138 - дешифратор 3х8

### Краткие сведения из теории

**Мультиплексор** — это комбинационная логическая схема, представляющая собой управляемый переключатель, который подключает к выходу один из информационных входов данных. Номер подключаемого входа равен числу (адресу), определяемому комбинацией логических уровней

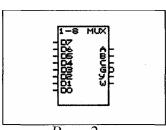

*Puc.* 2

на входах управления. Кроме информационных и управляющих входов, схемы мультиплексоров содержат вход разрешения, при подаче на который активного уровня мультиплексор переходит в активное состояние. При подаче на вход разрешения пассивного уровня мультиплексор перейдет в пассивное состояние, для которого сигнал на выходе сохраняет постоянное значение независимо от значений информационных и управляющих сигналов. Число информационных входов у мультиплексоров обычно 2, 4, 8 или 16. На puc.2 представлен мультиплексор 8х1 с инверсным входом разрешения G, прямым Y и инверсным W-выходами (W = Y).

На мультиплексоре можно реализовать логические функции, для чего нужно определить, какие сигналы и логические константы следует подавать на входы мультиплексора.

### Порядок проведения экспериментов Эксперимент 1. Исследование мультиплексора.

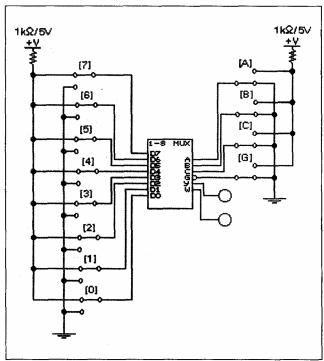

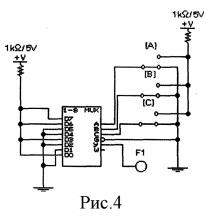

а). Откройте файл с13\_06 со схемой, изображенной на рис. 3.

Включите схему. С помощью ключа G установите на входе G мультиплексора уровень логического нуля. Поочередно подавая все возможные комбинации логических уровней при помощи ключей А, В, С на соответствующие входы мультиплексора, для каждой комбинации с помощью логических пробников определите, переключение какого из ключей в левой части схемы изменяет состояние выходов мультиплексора. Обозначение соответствующего входа мультиплексора запишите в таблицу 2 в разделе "Результаты экспериментов", указав при этом, как передается входной Рис.3

сигнал на выходы мультиплексора (напрямую или с инверсией). Например, если переключение ключа 4 изменяет состояние выходов мультиплексора, в таблице в строке с соответствующей комбинацией уровней сигналов на входах A, B, C следует записать для выхода Y - D4, для выхода W - D4.

б). Установите при помощи ключа G уровень логической единицы на входе G микросхемы. В раздел "Результаты экспериментов" запишите обозначения выводов, которые при переключении соответствующих ключей в левой части схемы не влияют на состояние выходов микросхемы.

### Эксперимент 2. Реализация заданной функции с помощью мультиплексора.

а). Определите значение функции F1 для каждой комбинации значений аргументов и заполните графу F1расч в разделе "Результаты экспериментов". Откройте файл c13\_08 со схемой, изображенной на рис. 4.

Включите схему. Подайте при помощи ключей A, B, C все возможные комбинации логических сигналов на входы мультиплексора и, определяя уровень сигнала на выходе Y логическим пробником F1, заполните графу F1a) в таблице 3 в разделе "Результаты экспериментов". Убедитесь, что функция, реализуемая мультиплексором, описывается выражением:

$$F1 = \overline{C} \overline{B} \overline{A} v B A v C B.$$

б). Откройте файл с13\_09 со схемой, изображенной на рис. 5.

Включите схему. Подавая в пошаговом режиме слова от генератора слов на входы мультиплексора и наблюдая уровень сигнала на выходе Y логическим пробником F1, заполните графу F16) в таблице 3 в разделе "Результаты экспериментов". Убедитесь, что сигнал на выходе также определяется функцией F1.

в). Откройте файл c13 10 со схемой, изображенной на рис. 6.

Последовательно подавая на входы схемы все возможные комбинации уровней логических сигналов, убедитесь, что уровень логической единицы на выходе появляется только в случаях, когда на входах схемы действуют комбинации, описываемые шестнад-цатеричными эквивалентами 07H, 09H, 0CH, ODH OFH, 13h, 17H, 19H, 1BH, 1C.H, 1DH, 1FH, при которых функция F2 принимает значение 1.

### Результаты экспериментов Эксперимент 1. Исследование мультиплексора.

| a) | Ta | аблица 2 |   |   |

|----|----|----------|---|---|

| A  | В  | C        | Y | W |

| 0  | 0  | 0        |   |   |

| 0  | 0  | 1        |   |   |

| 0  | 1  | 0        |   |   |

| 0  | 1  | 1        |   |   |

| 1  | 0  | 0        |   |   |

| 1  | 0  | 1        |   |   |

| 1  | 1  | 0        |   | _ |

| 1  | 1  | 1        |   |   |

б).

Выводы, не влияющие на состояние выходов микросхемы:

Измерение

### Эксперимент 2. Реализация заданной функции с помощью мультиплексора.

Таблица 3

| A | В | С | F1расч | Fla) | F16) |

|---|---|---|--------|------|------|

| 0 | 0 | 0 |        |      |      |

| 0 | 0 | 1 |        |      |      |

| 0 | 1 | 0 |        |      |      |

| 0 | 1 | 1 |        |      |      |

| 1 | 0 | 0 |        |      |      |

| 1 | 0 | 1 |        |      |      |

| 1 | 1 | 0 |        |      |      |

| 1 | 1 | 1 |        |      |      |

### Лабораторная работа №6

### **Исследование цифровых автоматов с памятью** 6.1. Триггеры

#### Цель

- 1. Изучение структуры и алгоритмов работы асинхронных и синхронных триггеров.

- 2. Исследование функций переходов и возбуждения основных типов триггеров.

- 3. Изучение взаимозаменяемости триггеров различных типов.

### Приборы и элементы

Генератор слов

Вольтметр

Логические пробники

Источник напряжения + 5 В

Источник сигнала "логическая единица"

Двухпозиционные переключатели

Двухвходовые элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ

RS и RS -триггеры

ЈК-триггер

**D**-триггер

#### Краткие сведения из теории

Триггер - простейшая цифровая схема последовательностного типа. В отличие от комбинационных схем состояние выхода Y которых в любой момент времени определяется только текущим состоянием входа X (Y = F(X)), состояние выхода триггера, как последовательностной схемы , зависит еще и от его внутреннего состояния Q:

$$Y=F(X,Q)$$

.

Другими словами, триггер является не только преобразователем, но и хранителем предшествующей и источником текущей информации (состояния). Это свойство обеспечивается наличием у него обратных связей.

Триггер имеет два устойчивых состояния: Q=1 и Q=0, поэтому его иногда называют бистабильной схемой. В каком из этих состояний окажется триггер, зависит от сигналов на входах триггера и от его предыдущего состояния, т. е. он имеет память. Можно сказать, что триггер является элементарной ячейкой памяти.

Тип триггера определяется алгоритмом его работы. В зависимости от алгоритма работы, триггер может иметь установочные, информационные и управляющие входы. Установочные входы устанавливают состояние триггера независимо от состояния других входов. Входы управления разрешают запись данных, подающихся на информационные входы. Наиболее распространенными являются триггеры RS, JK, D и T-типов.

Условия переходов триггеров из одного состояния в другое (алгоритм работы) можно описать табличным, аналитическим или графическим способами.

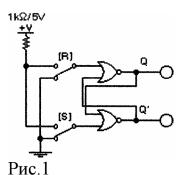

*Табличное описание* работы, например RS-триггера (рис. 1) <sup>№</sup> представлено в таблице 1 (таблица переходов) и таблице 2 (ха- Рис. 1 рактеристическая таблица).

Таблица 1

| 1111 |   |           |

|------|---|-----------|

| R    | S | $Q_{t+1}$ |

| 0    | 0 | Ot        |

| 0    | 1 | 1         |

| 1    | 0 | 0         |

| 1    | 1 | -         |

Таблица 2

| Qt | $Q_{t+1}$ | R | S |

|----|-----------|---|---|

| 0  | 0         | X | 0 |

| 0  | 1         | 0 | 1 |

| 1  | 0         | 1 | 0 |

| 1  | 1         | 0 | X |

В таблицах использованы следующие обозначения:

$Q_t$  - предшествующее состояние выхода;

$Q_{t+1}$  - новое состояние, устанавливающееся после перехода (возможно Qt+i=Qt);

- х безразличное значение сигнала: 0 или 1;

- - неопределенное состояние.

Аналитическое описание (характеристическое уравнение) можно получить из таблиц 1 и 2 по правилам алгебры логики:

$$Q_{t+1} = \overline{R} S v \overline{R} Q_t = \overline{R} (S v Q_t).$$

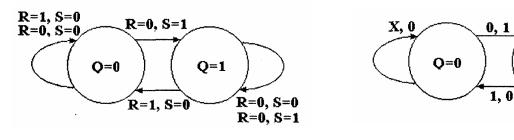

Зависимость  $Q_{t+1}$  от  $Q_t$  характеризует свойство запоминания предшествующего состояния. *Графическое описание* работы RS-триггера иллюстрируется графом *рис.3* (a,б).

Рис 3а Рис.36

График на рис. За показывает, что схема, которая находилась в состоянии Q==0, сохраняет это состояние как при воздействии входного набора R=0, S=0, так и при воздействии R=1, S=0. Если же на вход схемы, находящейся в состоянии Q=0, подействовать набором R=0, S=1, то она переходит в состояние Q=1 и сохраняет его при входных наборах R=0, S=1, либо R=0, S=0. На рис. Зб тот же граф триггера нарисован более компактно. Входные сигналы, которые могут принимать любые значения (как 0, так и 1), обозначены как X, а позиция обозначения соответствует последовательности R, S.

Аналогично, таблица переходов *(табл3)* и характеристическая таблица *(табл4)* JK-триггера имеют вид:

|   | 1 everturiyer 2 |      |  |

|---|-----------------|------|--|

| J | К               | Qt+i |  |

| 0 | O               | Ot   |  |

| 0 | 1               | О    |  |

| 1 | О               | 1    |  |

| 1 | 1               | Oi   |  |

Таблица 3

Таблица 4

| Qt | Qt+i | J | К |

|----|------|---|---|

| o  | o    | X | o |

| o  | 1    | 0 | 1 |

| 1  | О    | 1 | o |

| 1  | 1    | 0 | X |

Q=1

### Порядок проведения экспериментов Эксперимент 1. Исследование RS-триггера.

а). Откройте файл c14\_01 со схемой, изображенной на рис.1.

Включите схему. Последовательно подайте на схему следующие сигналы: S=0, R=1; S=0, R=0; S=1, R=0; S=0, R=0. Убедитесь в том, что:

- при S=0, R=1 триггер устанавливается в состояние Q=0;

- при переходе к S=0, R=0 триггер сохраняет прежнее состояние выхода Q=0;

- при S=1, R=0 триггер устанавливается в состояние Q=1;

- при переходе к 8=0, R=0 триггер сохраняет прежнее состояние выхода Q=1.

- 6.) Для каждого перехода (изменения состояния или сохранения предыдущего) нарисуйте в разделе "Результаты экспериментов" граф перехода. По результатам эксперимента заполните таблицу функций возбуждения для схемы рис. 1, приведенную в разделе "Результаты экспериментов" (maбn. 1).

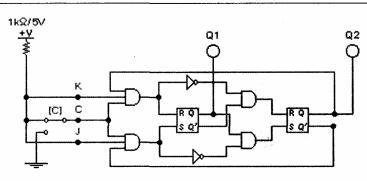

Эксперимент 2. Исследование JK-триггера, построенного на базе логических элементов и RS-триггеров.

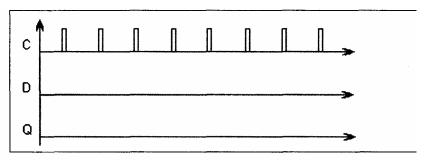

Откройте файл c14\_04 со схемой, изображенной на *puc. 2*. Включите схему. Изменяя уровень сигнала на входе C, составьте временные диаграммы сигналов на выходах Q1 и Q2 обоих RS-триггеров и зарисуйте их в разделе "Результаты экспериментов". Укажите режим работы триггера. Определите моменты изменения сигналов Q1 и Q2 по отношению к моментам изменения сигнала C. Отразите различие во временах переключения RS-триггеров на диаграммах.

Рис.2

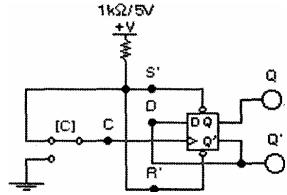

### Эксперимент 3. Исследование D-триггера.

а). Откройте файл с14\_05 со схемой, изображенной на рис. 3. Включите схему.

#### Убедитесь в том, что:

- при R=1, S=0 триггер устанавливается в 1 (Q=1, Q'=0) независимо от состояния остальных входов;

- при R=0, S=1 триггер устанавливается в 0 (Q=0, Q'=1) независимо от состояния остальных входов.

- 6). Установите S' = R' = 1, проверьте истинность характеристической таблицы триггера, по Puc.3 результатам эксперимента заполните таблицу 2 в разделе "Результаты экспериментов".

- *в*). Составьте временные диаграммы работы триггера для всех возможных комбинаций Qt, Dt и зарисуйте их в раздел "Результаты экспериментов .

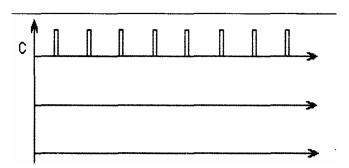

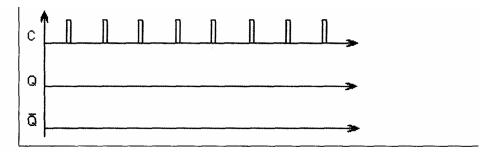

### Эксперимент 4. Исследование работы D-триггера в счетном режиме.

Соберите схему, изображенную на рис. 4.

Подавая на счетный вход С тактовые импульсы с помощью ключа [С] и определяя состояние выходов триггера при помощи пробников, составьте временные диаграммы работы триггера в счетном режиме и занесите их в раздел "Результаты экспериментов".

וסו

(C)

(R)

D

R.

Рис.4

### Результаты экспериментов Эксперимент 1. Исследование RS-триггера

| Графы переходов.<br>Состояние входов | Граф перехода | Характеристическая |    |      | <b>таблица</b><br>Таблица 1 |  |   |

|--------------------------------------|---------------|--------------------|----|------|-----------------------------|--|---|

| S=0, R=1                             |               |                    | Qt | Qt+i | R                           |  | S |

| при переходе к S=R=0                 |               |                    | 0  |      | 0                           |  | 0 |

| при переходе к в к о                 |               |                    | 0  |      | 0                           |  | 0 |

|                                      |               |                    | 1  |      | 1                           |  | 0 |

| при R=1, S=0                         |               |                    | 1  |      | 0                           |  | 0 |

|                                      |               |                    | 1  |      | 0                           |  | 1 |

при переходе к S=R=0

Эксперимент 2. Исследование JK-триггера, построенного на базе логических элементов и RS-триггеров.

Диаграмма работы триггера.

Эксперимент 3. Исследование D-триггера.

б). **Характеристическая таблица** Таблица 2.

| Qt | Qt+i | J | К |

|----|------|---|---|

| 0  |      | 0 | 0 |

| 0  |      | 0 | 1 |

| 0  |      | 1 | 0 |

| 0  |      | 1 | 1 |

| 1  |      | 0 | 0 |

| 1  |      | 0 | 1 |

| 1  |      | 1 | 0 |

| 1  |      | 1 | 1 |

### Диаграмма работы триггера

### Эксперимент 4. Исследование работы D-триггера в счетном режиме.

Диаграмма работы триггера.

#### Вопросы

- 1. Является ли элементом памяти выключатель настольной лампы?

- 2. Если продолжить предыдущий вопрос, то как можно охарактеризовать:

- а) кнопочный выключатель (один раз нажал лампа горит; второй раз нажал лампа погасла);

- б) клавишный переключатель-коромысло: нажал на одно плечо лампа зажглась или продолжает оставаться горящей; нажал на другое плечо погасла. Аналогия с какими видами триггеров напрашивается?

- 3. Чем отличается работа RS-триггера с прямыми входами от работы RS-триггера с инверсными входами?

- 4. Почему комбинация сигналов 11 на входах RS-триггера называется «запрещенной»?

- 5. В чём отличие таблицы переходов триггера от характеристической таблицы?

- 6. Как свойство запоминания отражается в характеристических уравнениях триггеров?

- 7. В чём отличие работы синхронных триггеров от асинхронных?

- 8. Какова приоритетность информационных и установочных входов в синхронных триггерах?

- 9. Почему JK-триггер при J=K=1 не превращается в автогенератор?

- 10. Почему Т-триггер получил название счетного? Какое число импульсов он может сосчитать?

- 11.Как работает D-триггер, если D==Q?

### 6.2. Счетчики

### Цель

- 1. Изучение структуры и исследование работы суммирующих и вычитающих счетчиков.

- 2. Изучение способов изменения коэффициента пересчета счетчиков.

- 3. Исследование работы счетчиков с коэффициентом пересчета, отличным от  $2^n$ .

### Приборы и элементы

Генератор слов

Логический анализатор

Логические пробники

Источник напряжения + 5 В

Генератор тактовых импульсов

Источник сигнала "логическая единица"

Двухпозиционные переключатели

Базовые двухвходовые логические элементы

Базовые триггеры RS, JK и D-типов

### Краткие сведения из теории.

Счетчик - устройство для подсчета числа входных импульсов. Число, представляемое состоянием его выходов по фронту каждого входного импульса, изменяется на единицу. Счетчик можно реализовать на нескольких триггерах. В суммирующих счетчиках каждый входной импульс увеличивает число на его выходе на единицу, в вычитающих счетчиках каждый входной импульс уменьшает это число на единицу. Наиболее простые счетчики - двоичные.

Счетчики можно реализовать на триггерах. При этом триггеры соединяют последовательно. Выход каждого триггера непосредственно действует на тактовый вход следующего. Для того, чтобы реализовать суммирующий счетчик, необходимо счетный вход очередного триггера подключать к инверсному выходу предыдущего. Для того, чтобы изменить направление счета (реализовать вычитающий счетчик), используют следующие способы:

- а). Считывание выходных сигналов счетчика не с прямых, а с инверсных выходов триггеров.

- б). Изменение структуры связей в счетчике. Подача на счетный вход

следующего триггера сигнала не с инверсного, а с прямого выхода предыдущего триггера.

### Порядок проведения экспериментов

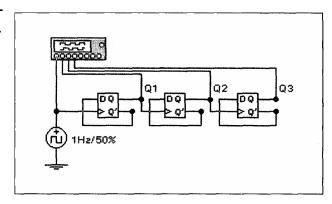

### Эксперимент 1. Исследование вычитающего счетчика.

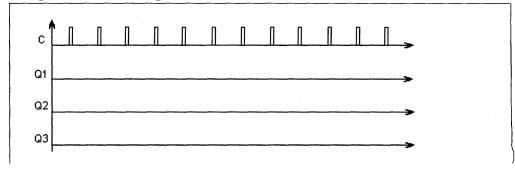

- *а)*. Откройте файл c14\_07 со схемой, изображенной *на. рис. 5*. Включите схему. Зарисуйте временные диаграммы работы вычитающего счетчика в раздел "Результаты экспериментов".

- б). В схеме на рис. 5 входы логического анализатора подключите к инверсным входам триггеров. Включите схему. Зарисуйте полученные временные диаграммы в раздел "Результаты экспериментов" и сравните их с диаграммами, полученными в эксперименте 1.

Рис.5

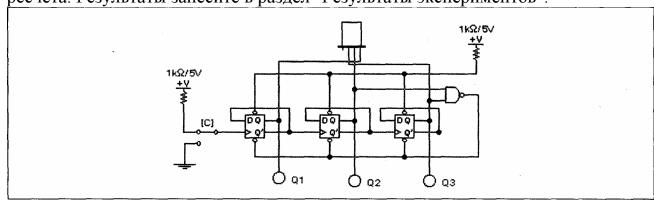

### Эксперимент 2. Исследование счетчика с измененным коэффициентом пересчета.

а). Откройте файл c14\_08 со схемой, изображенной на рис. 6. Включите схему. Подавая на вход схемы тактовые импульсы при помощи ключа С и наблюдая состояние выходов счетчика при помощи логических пробников, составьте временные диаграммы работы счетчика и определите коэффициент пересчета. Результаты занесите в раздел "Результаты экспериментов".

*Puc.* 6

### Эксперимент 3. Исследование регистра Джонсона.

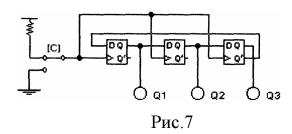

Откройте файл c14\_09 со схемой, изображенной на *puc.* 7. Счетное устройство, приведенное на рисунке, по-

Джонсона или регистра с перекрестными связями. Включите схему. Постройте временные диаграммы сигналов на выходах триггеров. Определите коэффициент пересчета регистра Джонсона. Результаты занесите в раздел "Результаты экспериментов".

### Результаты экспериментов

Эксперимент 1. Исследование вычитающего счетчика.

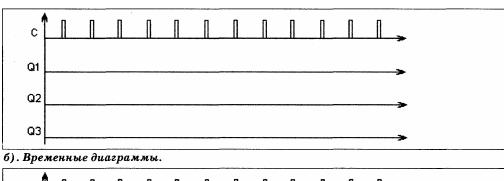

а). Временные диаграммы.

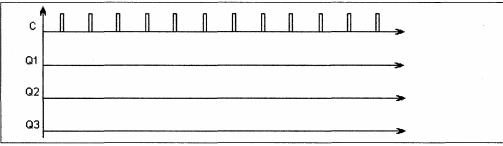

Эксперимент 2. Исследование счетчика с измененным коэффициентом пересчета.

Временные диаграммы.

Эксперимент 3. Исследование регистра Джонсона.

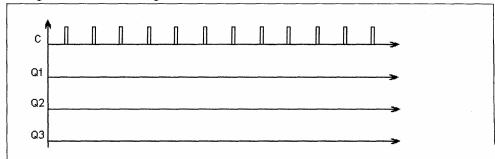

Временные диаграммы.

### Вопросы.

- 1. Почему при подключении счетных входов триггеров к инверсным выходам предыдущих каскадов счетчик на D-триггерах работает как суммирующий, а при подключении к прямым -как вычитающий?

- 2. В каком режиме будет работать счетчик на JK-триггерах при подключении счетных входов триггеров к прямым выходам предыдущих каскадов? Как изменится режим работы счетчика при подключении счетных входов триггеров к инверсным выходам?

- 3. Какой коэффициент пересчета имеет регистр Джонсона?

- 4. Какими способами можно изменить коэффициент пересчета счетчика?

- 5. Сколько триггеров должен содержать счетчик с коэффициентом пересчета Ксч <sup>=</sup> {3, 5, 7, 9, 10,12,14,15,24,30}?

- 6. В двоичном счетчике коэффициент пересчета равен 8, число триггеров 3. При поступлении тактовых импульсов на счетный вход счетчик изменяет своё состояние в следующей последовательности: 000-001-010-011-100-101-110-111-000. Сколько триггеров в счетчике изменяют свое состояние одновременно на каждом из переходов? Действительно ли триггеры изменяют своё состояние одновременно? Как происходит переход счетчика из состояния 111 в

состояние 000? Какой из триггеров первым изменит своё состояние? Что послужит причиной переключения второго триггера? Как развивается процесс изменения состояния триггеров при переходе счетчика из состояния 011 в состояние 100?

7. Какую разрядность должен иметь счетчик, отсчитывающий секунды и десятки секунд при наличии генератора импульсов частотой 10 кГц?

### Литература.

- 1. Вычислительные машины, системы, сети и телекоммуникации: Учебник/ А.П.Пятибратов, С.Н.Беляев и др.; Под ред. проф. А.П.Пятибратова.- М.: Финансы и статистика, 1998.- с.: ил.

- 2. Чернов В.Г. Математические и логические основы вычислительных машин. Методические указания к самостоятельной работе студентов. -ВПИ, 1992-47 с.